Hardmask, HAR channel hole and slit etch profile metrology for real-time process feedback

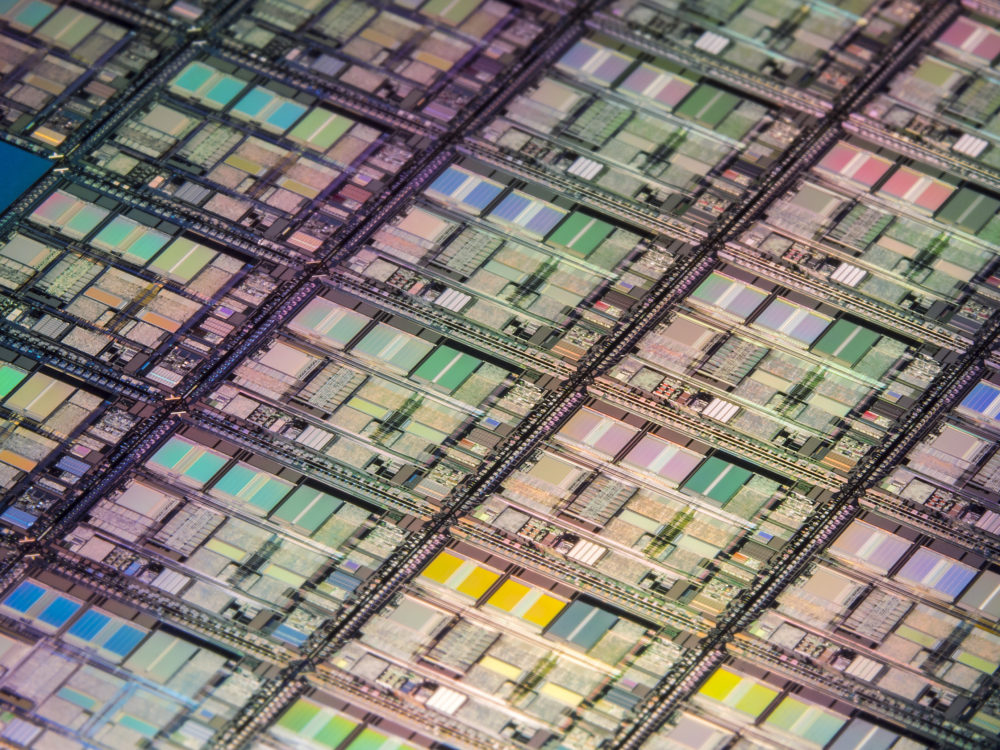

As the number of layers in 3D NAND increases, hardmasks are used for etching deep, high aspect ratio (HAR) features that conventional photoresists cannot withstand. Monitoring hard mask thickness is critical to the 3D NAND process as it goes through an iterative etch process. Film thickness and repeatability affects the active area of cell and consistency of the litho/etch performance. Improved device performance and yield rely on the ability to accurately measure these layers and understand the correlation to the deposition and etch processes.

In addition, etching HAR features like channel hole and slit (word line cut) is posing a large challenge in 3D NAND process control. Monitoring HAR hole and trench profile and tilt/twist is critical to the 3D NAND process as an uncontrolled etch profile variation causes device short, reduced channel mobility and loss of yield. The ability to accurately measure the HAR etch profile for real-time process control is critical to device performance and yield.