3D NAND Needs 3D Metrology

You’ve read the reports: the memory market is floundering as the semiconductor industry moves through another scarcity/surplus cycle.

Be that as it may, innovation is happening as the industry continues to pursue increasingly higher three-dimensional stacks, with 3D NAND stacks taller than 200 layers entering production.

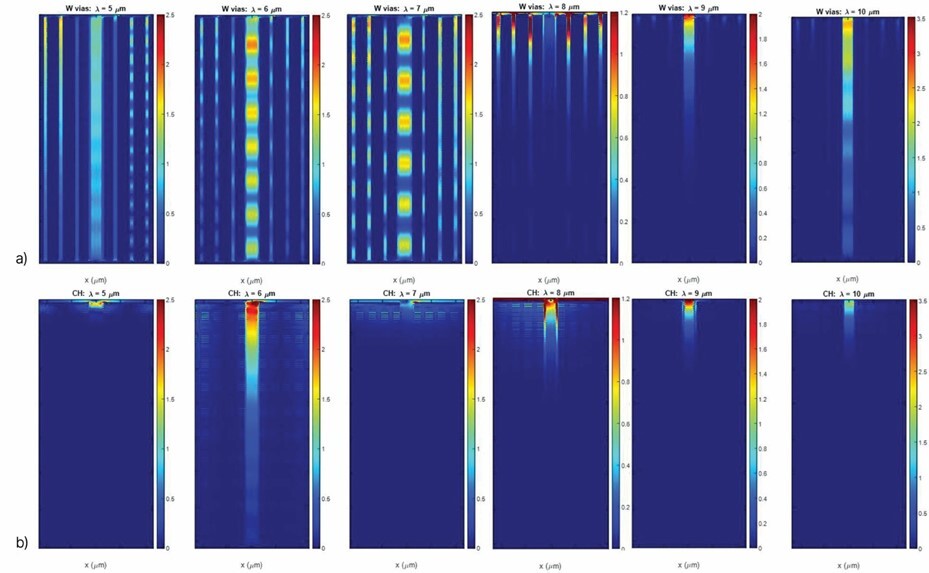

However, there are challenges. Among those: conventional optical critical dimension (OCD) metrology systems have difficultly measuring the tungsten (W) recess in the wordline (WL) slit following the replacement gate step. This is particularly a problem as high-aspect ratio (HAR) stacks reach 96 layers or higher. For manufacturers, the ability to measure the W recess is critical. Under-etching the W replacement gates in the recess can cause wordlines to short, while over-etching the W gates can damage cells or cause a short from the wordline to the source line.