Heterogeneous Integration: Exposing Large Panels with Fewer Shots

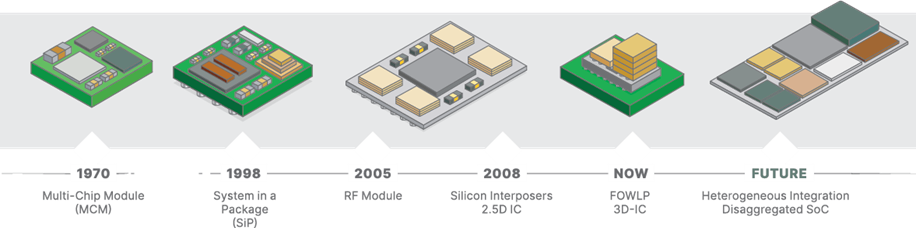

The More than Moore era is upon us, as manufacturers increasingly turn to back-end advances to meet the next-generation device performance gains of today and tomorrow. In the advanced packaging space, heterogeneous integration is one tool helping accomplish these gains by combining multiple silicon nodes and designs inside one package.

But as with any technology, heterogeneous integration, and the fan-out panel-level packaging that often enables it, comes with its own set of unique challenges. For starters, package sizes are expected to grow significantly due to the number of components making up each integrated package. The problem: these significantly bigger packages require multiple exposure shots to complete the lithography steps for the package. Adding to this, multiple redistribution layers (RDL) may cause stress to both the surface and inside of the substrate, resulting in warpage. And then there is the matter of tightening resolution requirements and more stringent overlay needs.