Blog Post posted on Nov 8, 2022

For high-performance computing, artificial intelligence, and data centers, the path ahead is certain, but with it comes a change in substrate format and processing requirements. Instead of relying on the quest for the next technology node to bring about future device performance gains, manufacturers are charting a future based increasingly on heterogeneous integration.

But while heterogeneous integration promises more functionality, faster data transfer, and lower power consumption, these chiplet combinations, with different functionalities and nodes, will require increasingly larger packages, with sizes at 75mm x 75mm, 150mm x 150mm, or even larger.

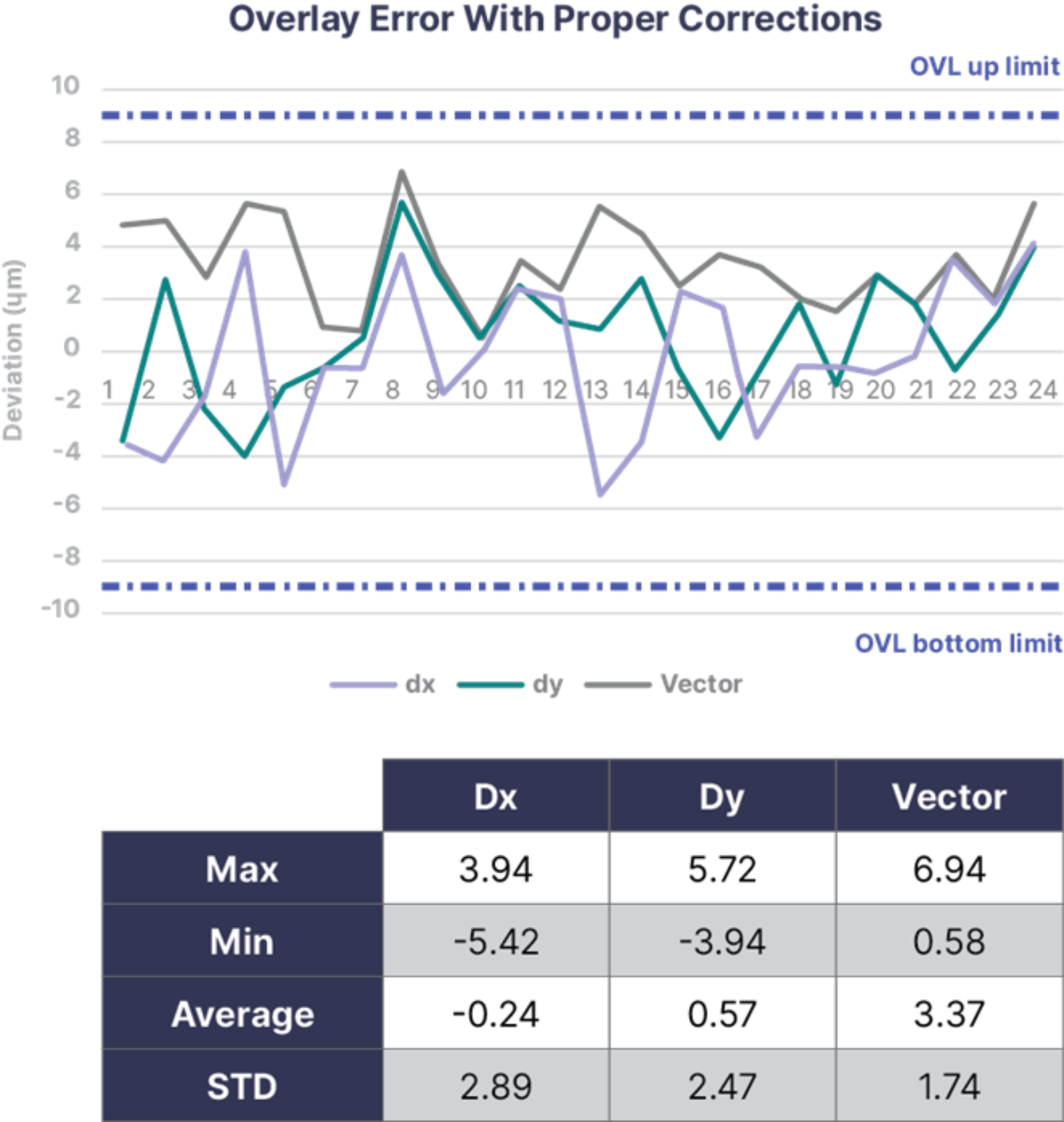

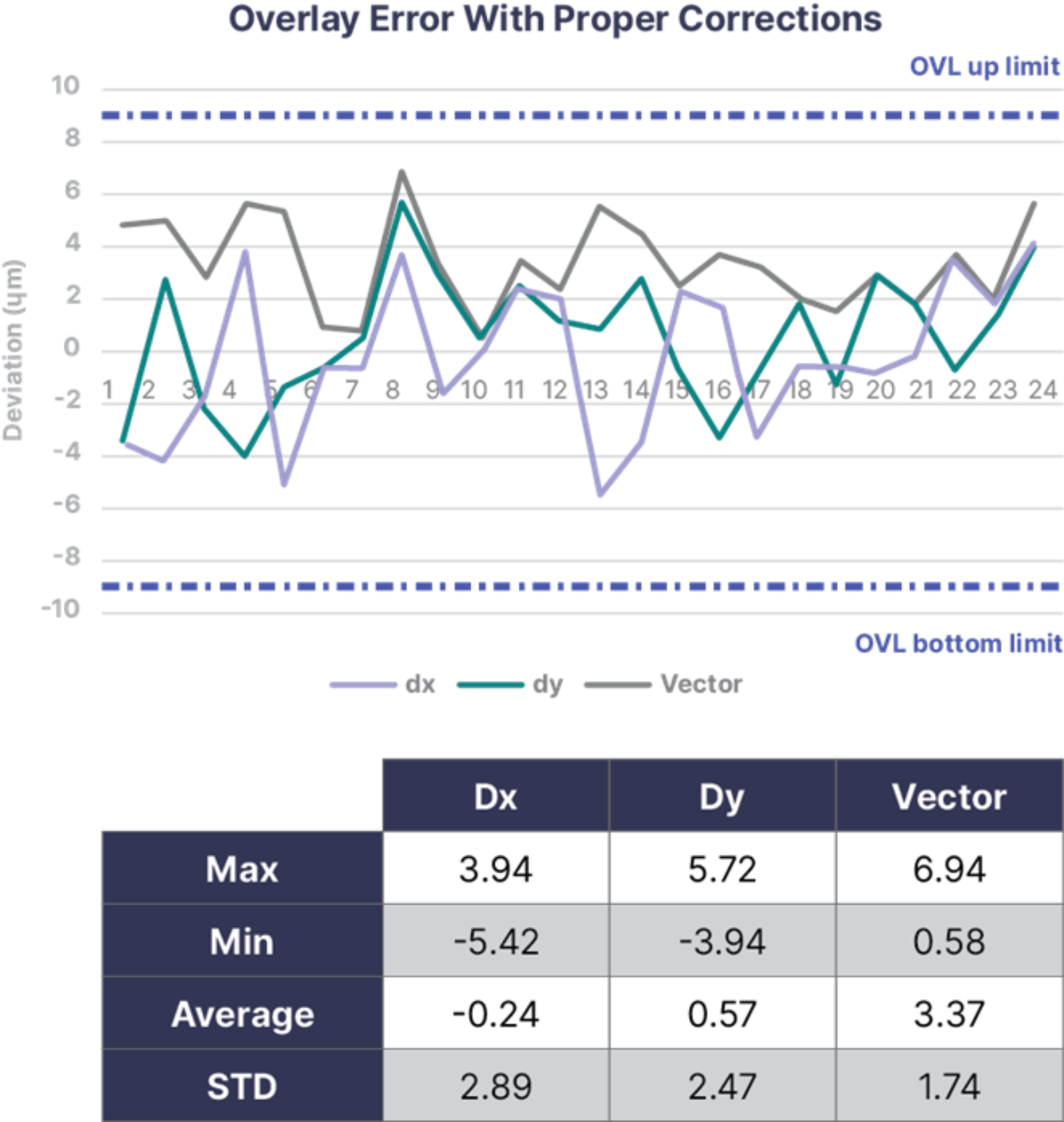

To further complicate matters, these packages will also feature elevated numbers of redistribution layers, in some cases as high as 24 layers. And with each of those layers, the threat of a single killer defect, which would effectively ruin an entire package, increases. As such, the ability to maintain high yields becomes increasingly difficult.