Dragonfly® G3 System

The Dragonfly G3 system is resetting the industry’s expectations for throughput, accuracy and reliability. Combining 2D and 3D technologies, the system detects yield-robbing defects and measures features critical for today’s semiconductor technologies

Product Overview

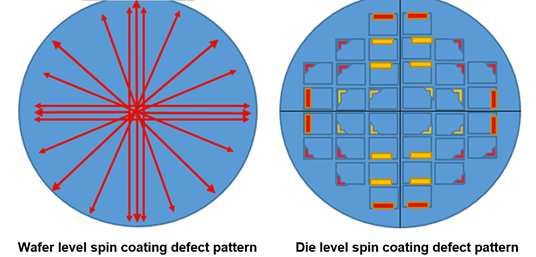

The Dragonfly G3 is a widely adopted pattern inspection system that utilizes line scan imaging technology to deliver fast, sub-micron defect detection for both R&D and high volume manufacturing environments. It features multiple illumination channels, including brightfield, darkfield, high-speed IR for embedded defects, and Clearfind® technology for detecting non-visual organic residues. Powered by modern machine learning algorithms, the Dragonfly G3 system offers a complete on-tool solution for defect detection, nuisance reduction and classification.

The system offers additional flexibility through the integration of multiple 3D metrology capabilities, including film thickness and structural profiling, and substrate thickness measurement. It features the latest 3Di™ technology, delivering and precise bump height metrology. The Dragonfly G3 system, with optional edge and backside inspection via the EB40 module, offers a comprehensive all-surface inspection solution for both front-end and back-end OQA.

Applications

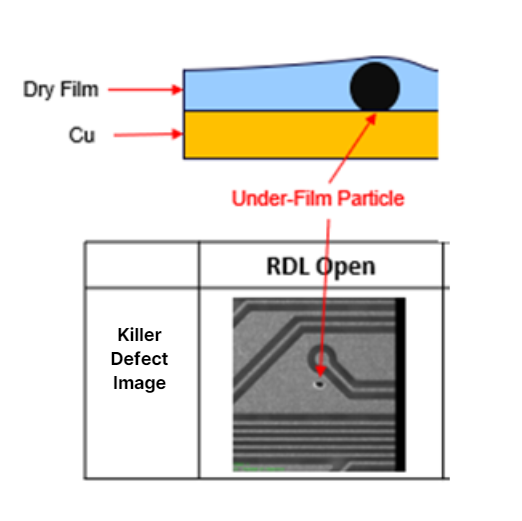

- Redistribution layers (RDL): after develop, after etch

- Reconstructed and bonded wafers

- Micro bumps and Cu pillars

- Post saw

- Gel and waffle pack inspection

- Post probe and testing

- OQA

Featured Markets

Hybrid Bonding Process Control Solution

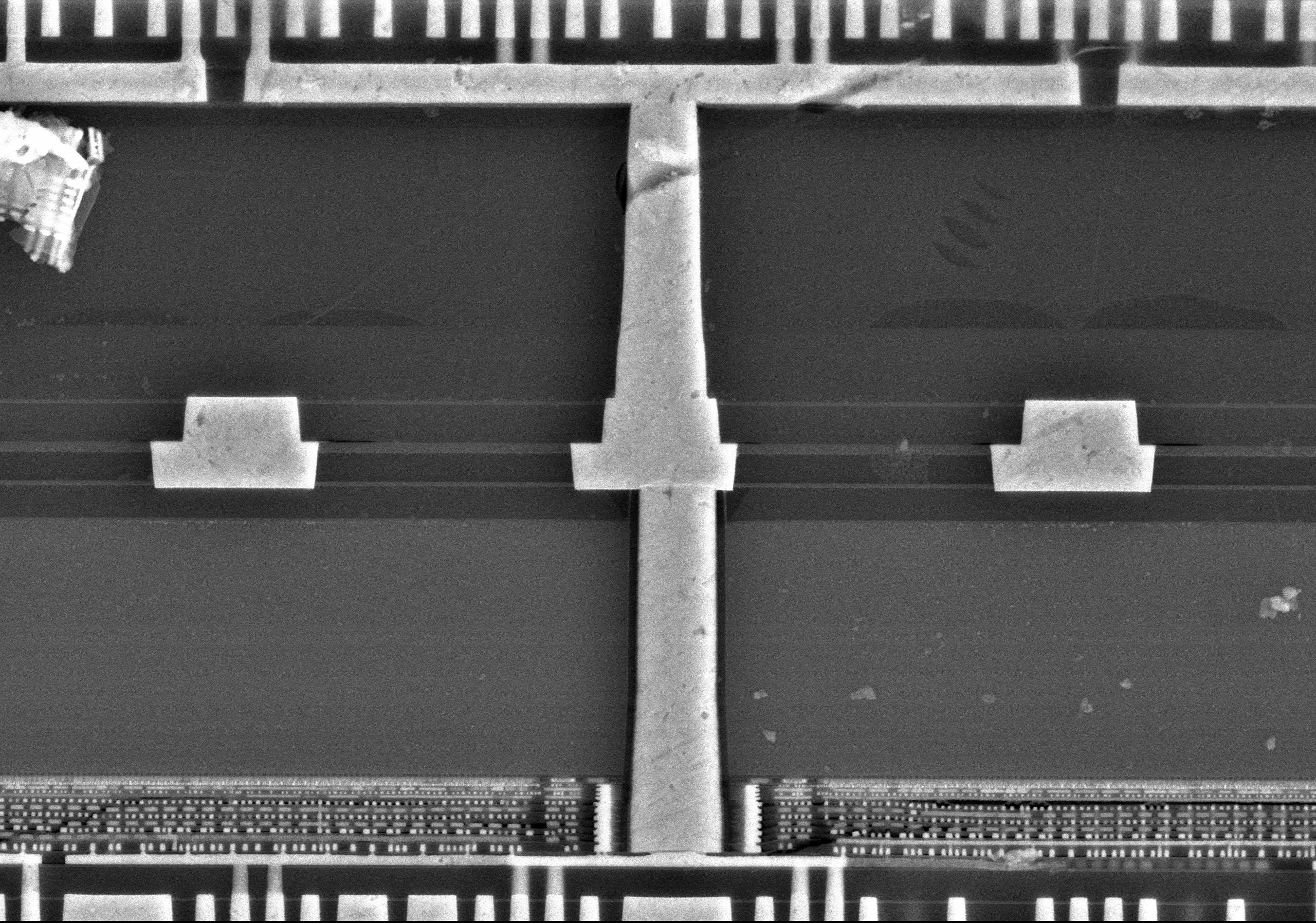

Hybrid bonding enables ultra-dense 3D memory interconnects with up to 1,000x more connections than microbumps. Achieving high yield requires stringent process control, including monitoring topography and detecting particles, cracks and voids. Measuring dishing in copper pads provides valuable insight into surface conditions. Together, these process control insights contribute to improved device reliability and performance.

Enabling In-Line Process Control for Hybrid Bonding Applications

As demand grows for high-performance computing (HPC) and AI-driven applications, manufacturers are turning to hybrid bonding to enable the ultra-dense 3D integration required for next-generation chip architectures. This advanced packaging technology presents significant process challenges. Surface preparation must be precisely controlled to eliminate particles, excess recess, and copper pad dishing, all of which can compromise bond quality. During pre-annealing, particle-induced gaps and wide bonding gaps can prevent proper wafer contact. Post-annealing, the formation of dielectric and metal voids introduces further risks to electrical performance and long-term reliability.

Do you have a Dragonfly G3 system question? Let’s talk!

As your partner for innovative solutions, we’re always here for you.

Discover how our cutting-edge semiconductor solutions are engineered to meet your most complex challenges: delivering performance, reliability and innovation where it matters most.

Let’s Talk

"*" indicates required fields