EB40™ Module

The EB40 Module combines edge and backside inspection into one tool with the option to be paired with an inspection system to provide a high throughput all surface inspection solution.

Product Overview

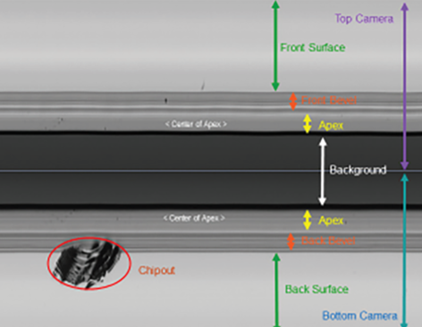

The Class 1 certified EB40 module offers combined edge and backside inspection and is also available as separate edge (E40) and backside (B40) modules. These modules provide brightfield and darkfield inspection to detect defects on the entire bevel and backside, covering Zone 1 to Zone 5. This enables faster root-cause analysis of defects that can migrate to the wafer interior, impacting die yield.

The EB40 module captures defect images on the fly, creates whole-wafer composite images, and integrates with SEM bevel review. All inspection and metrology results, including defect, whole wafer and SEM images can be analyzed together in a single database using Discover Defect software. Correlating EBR metrology with defectivity data, SEM data and micro-inspection results is just the beginning of what Discover software can do. In addition to advanced on-tool defect binning, real-time edge ADC classification can be assigned to defects prior to manual offline review using Discover Review software.

Applications

- EDGE INSPECTION

- Lithography process monitoring

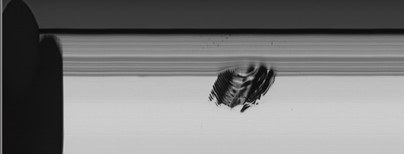

- Cracks/Chips, Slurry, cleaning contaminants and residual films

- EBR Metrology

- Bonded wafer adhesive inspection

- BACKSIDE INSEPCTION

- Scratches

- Chuck and end effector signatures

- Backside particles and residues

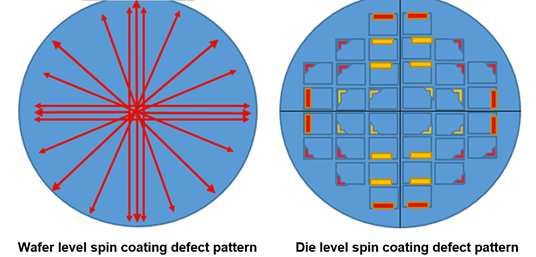

- Wafer level pattern detection

Featured Markets

Do you have an EB40 module question? Let’s talk!

As your partner for innovative solutions, we’re always here for you.

Discover how our cutting-edge semiconductor solutions are engineered to meet your most complex challenges: delivering performance, reliability and innovation where it matters most.

Let’s Talk

"*" indicates required fields

Firefly® G3 System

The Firefly G3 system provides automated inspection and 3D metrology for advanced IC substrates and panel level packaging, delivering high resolution and productivity for demanding applications like high-performance computing (HPC), artificial intelligence (AI), cloud computing and machine/deep learning.

Product Overview

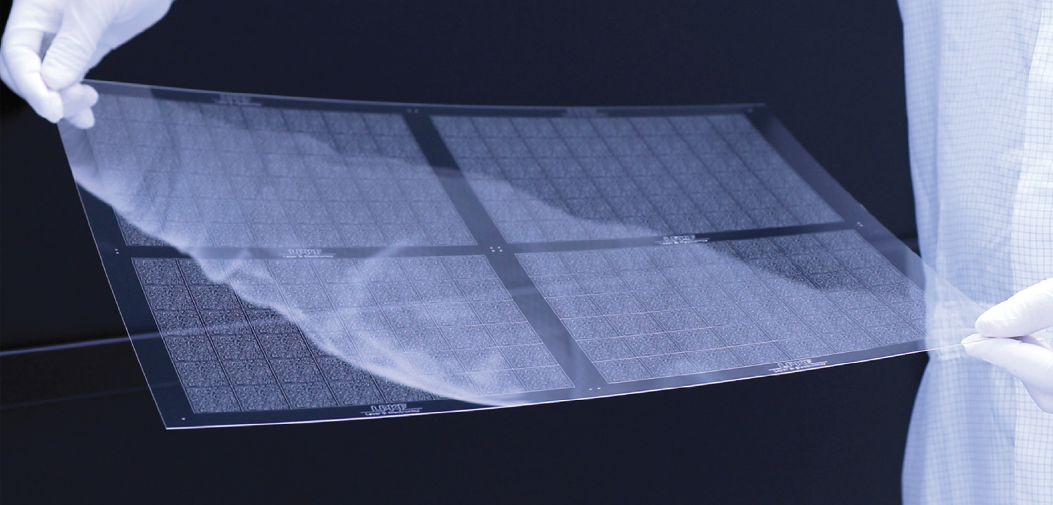

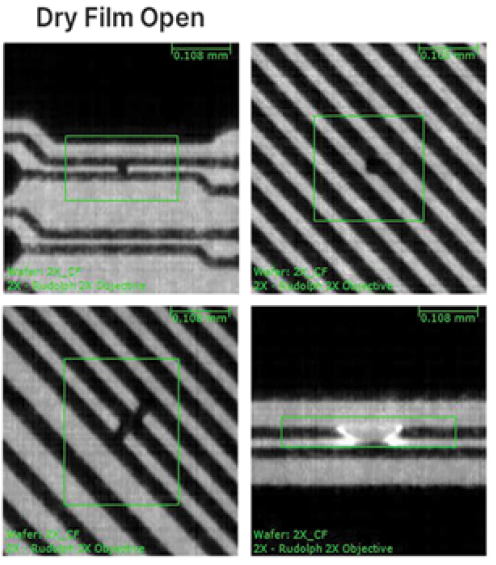

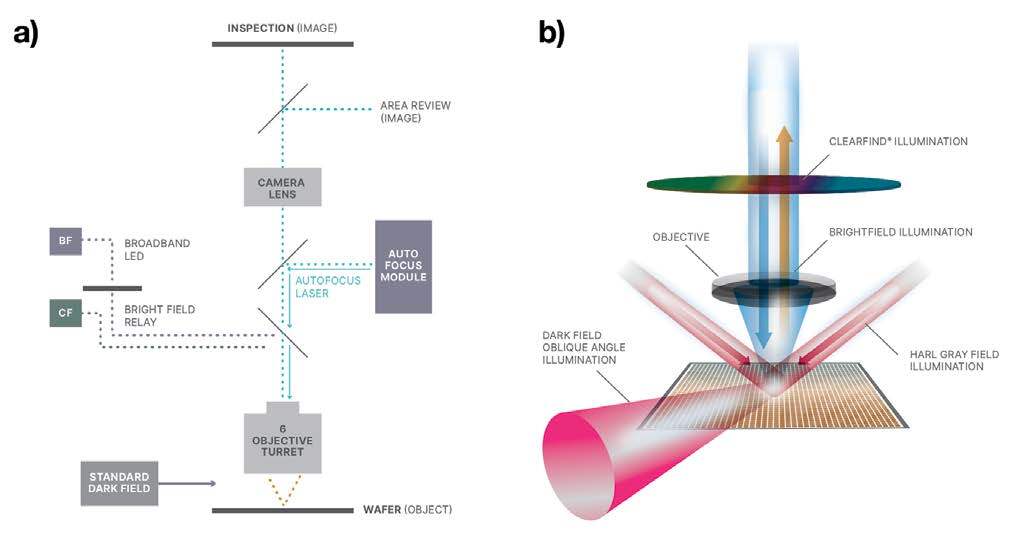

The Firefly G3 platform offers multiple imaging modes, including Onto Innovation’s patented Clearfind® Technology, a technique to detect residue defects on metal and metal defects on organic layers. The combination of high sensitivity inspection, 2D/3D metrology and on tool color image capture capability in a single platform reduces capital investment requirements and provides a reliable pathway for panel-based process applications that require high I/O counts and multiple-chip integration.

Integration with Onto Innovation’s Discover® Defect and TrueADC® software quickly turns defect data into actionable process control, improves defect classification and reduces manual review. It enables our customers to develop, learn and analyze new processes reliably while significantly improving their product delivery time to market.

Applications

- Advanced IC Substrates (AICS): CCL and Glass

- Fan-out Panel Level Packaging (FOPLP)

- Interposers

- Embedded Die substrates/ Interposer

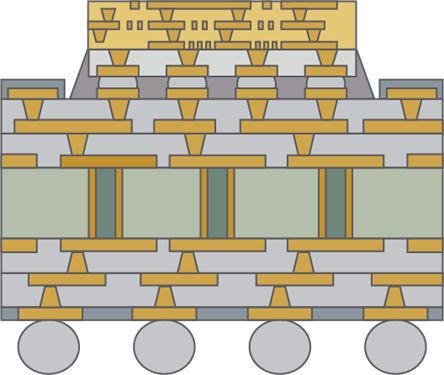

- 2.5D/3D integration

Featured Markets

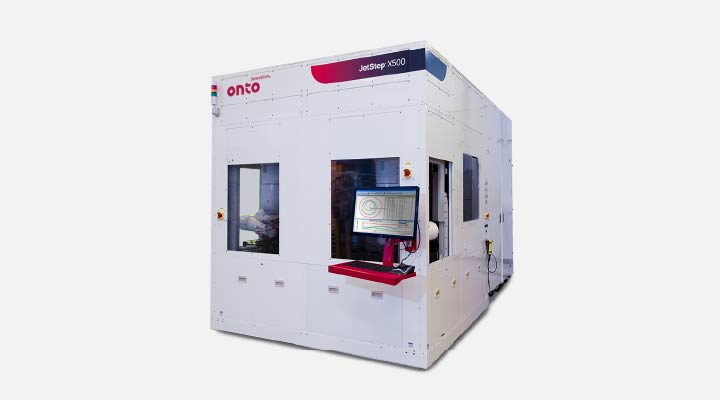

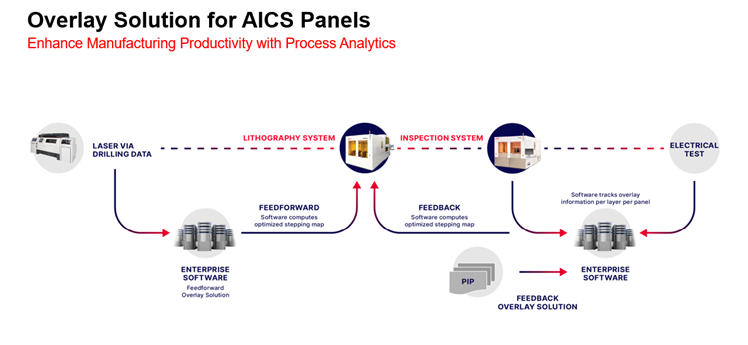

Adaptive Shot Lithography Solution

Die shift on reconstituted panels can significantly impact both productivity and yield. To address this challenge, we use a parallel die placement measurement process and advanced analytics to provide a means to balance productivity against yield. Our integrated lithography cell, featuring Firefly inspection, StepFAST software, and JetStep Lithography, delivers industry-leading throughput and yield for fan-out panel level packaging.

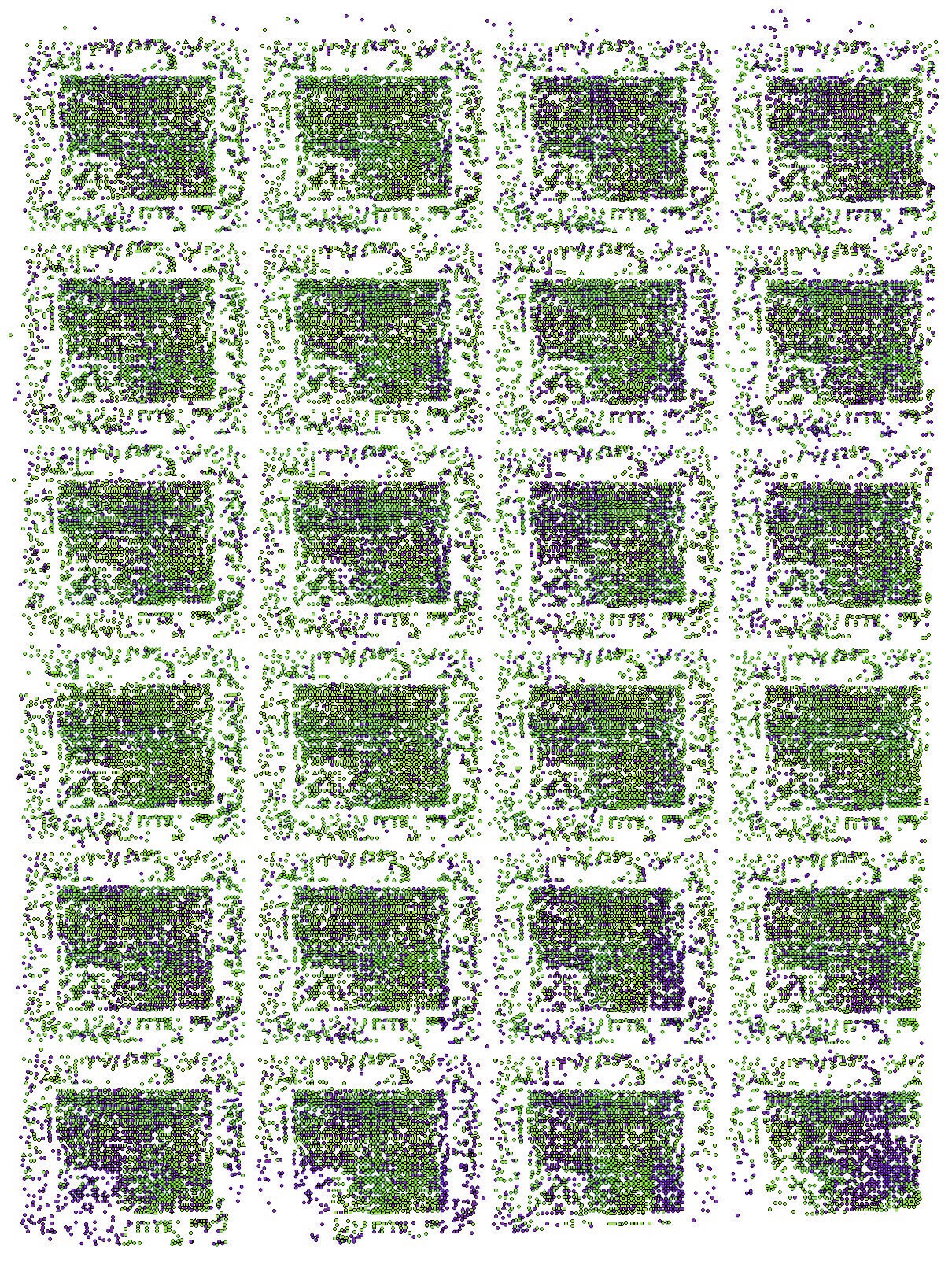

Overcoming FOPLP Die Placement Error

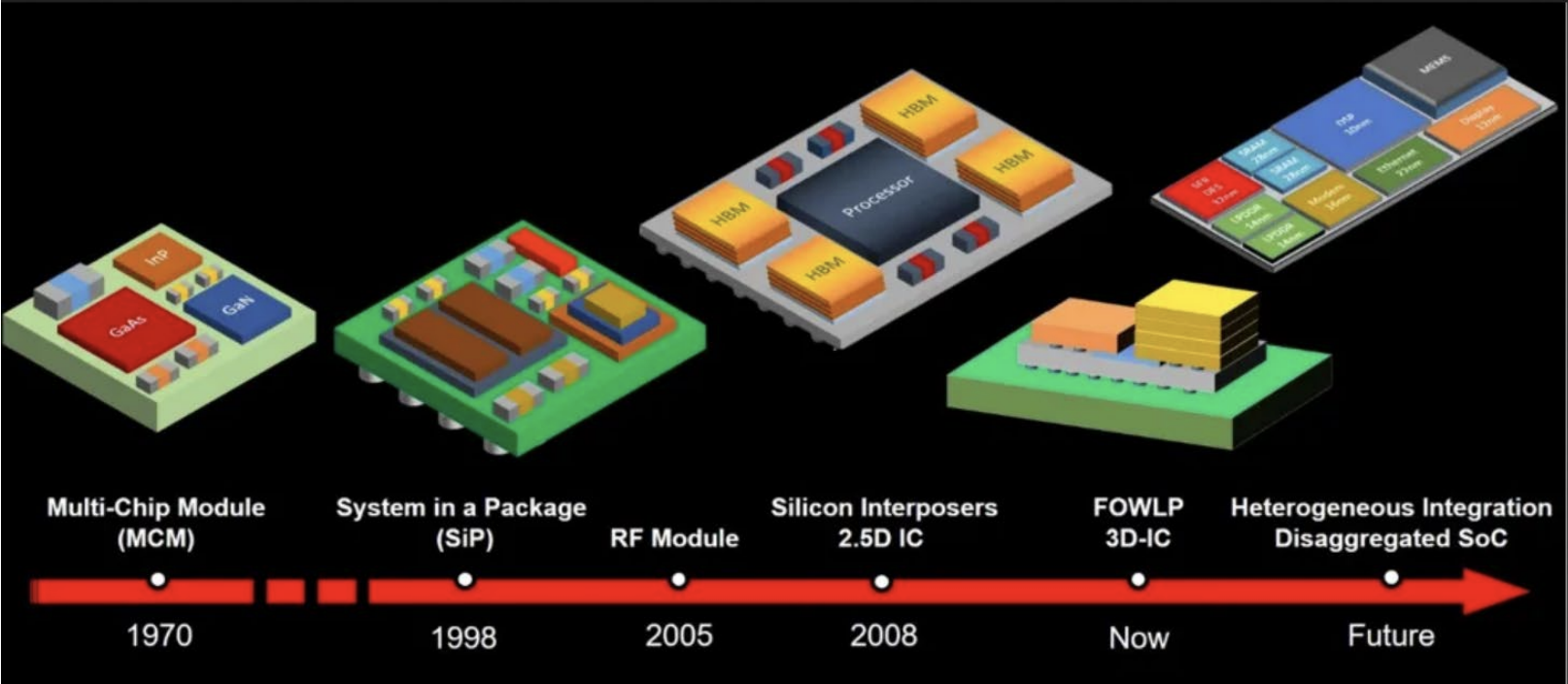

It is well understood that advanced packaging applications require high performance, low cost, increased functionality and improved reliability that 2.5D and 3D packaging solutions provide. Fan-out panel-level packaging (FOPLP) is one of the technologies that has the potential to meet these packaging requirements.

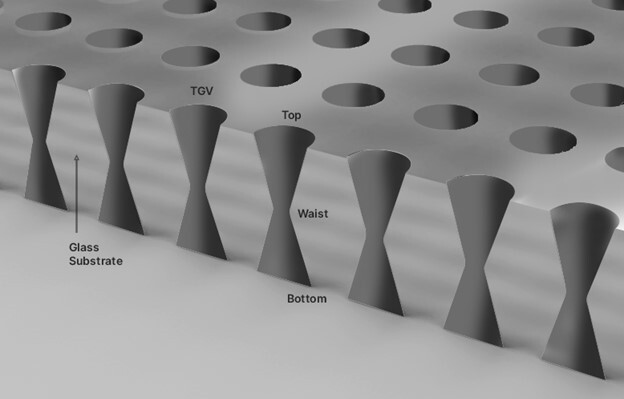

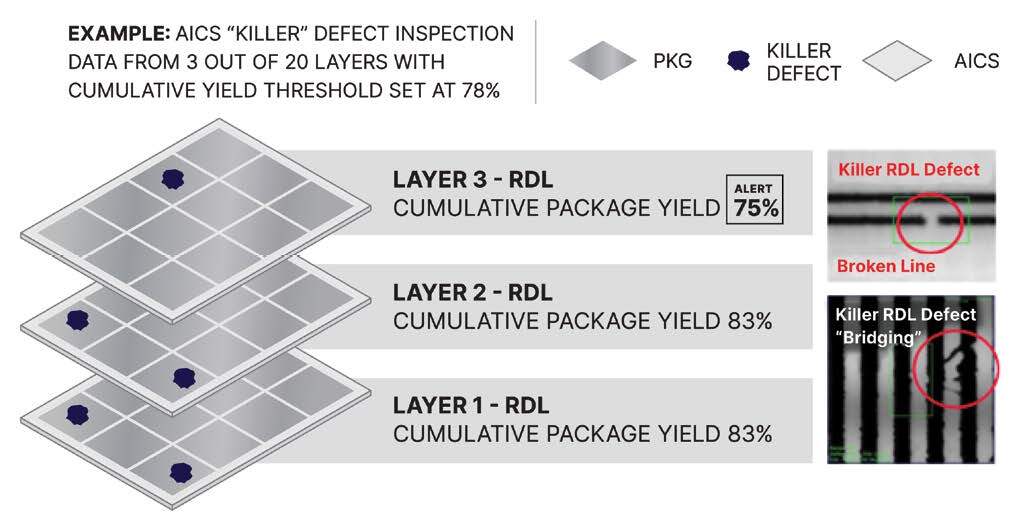

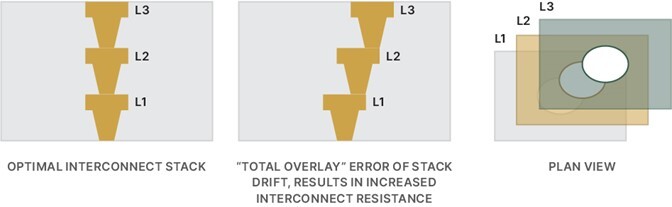

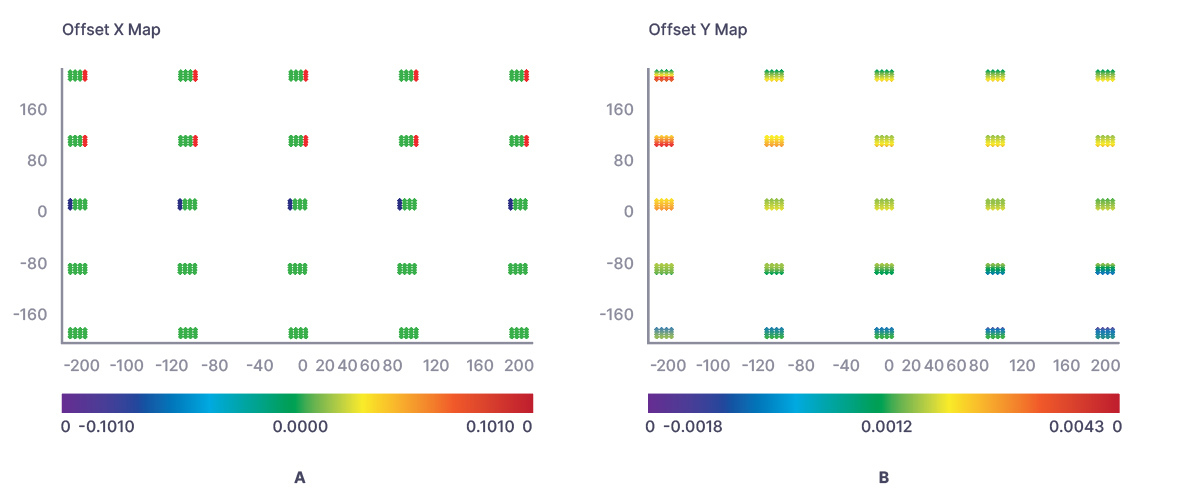

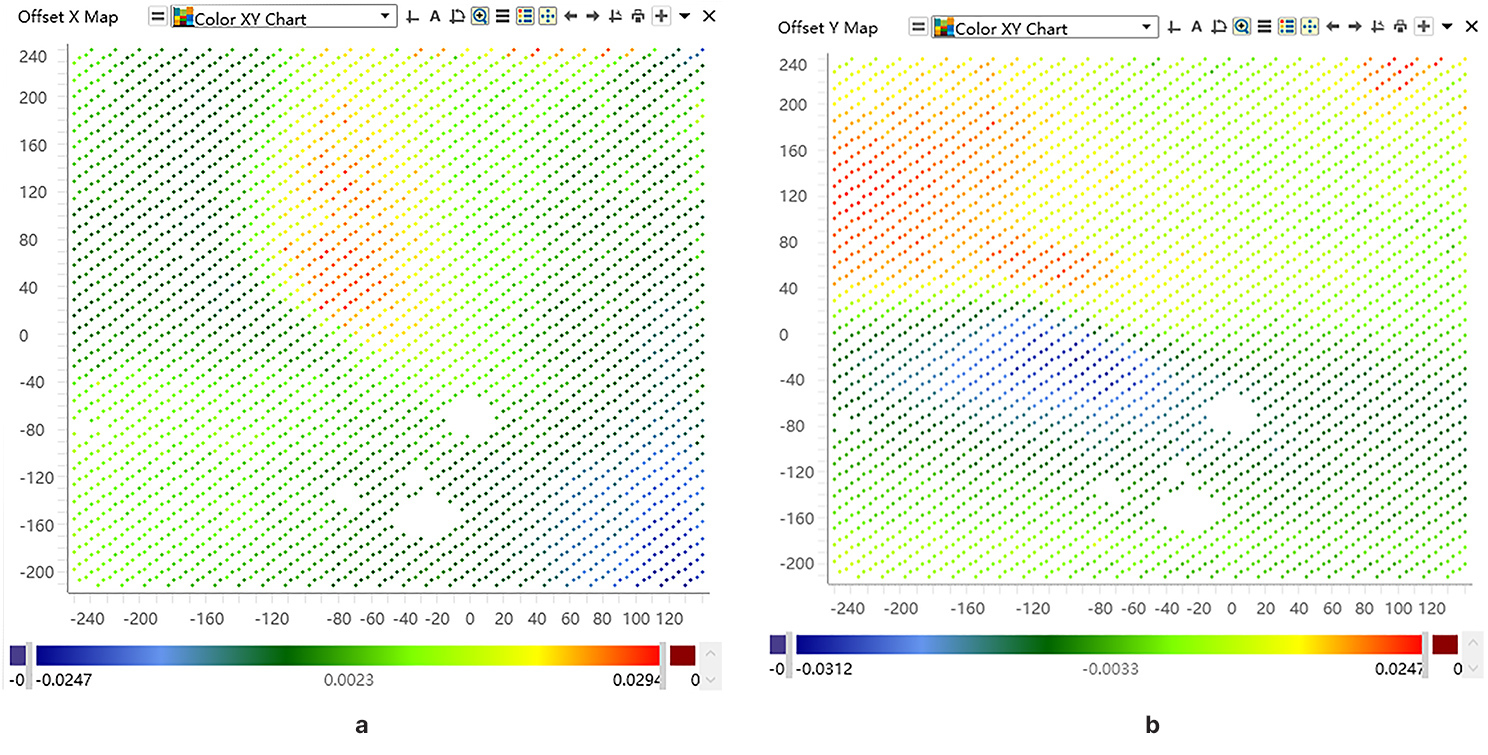

Adaptive Overlay Control

During the processing of organic (CCL) advanced IC substrates (AICS) the substrates become distorted which impacts the overlay of Via to RDL pad structures. To solve this problem, the stepper must adjust the alignment solution to match the previous layer’s distortion by measuring the overlay. Proprietary software provides the user with the ability to adjust each zone of the AICS with independent offsets.

Analysis of Pattern Distortion by Panel Deformation

The growing demand for heterogeneous integration is driven by the 5G market. This includes smartphones, data centers, servers, high-performance computing (HPC), artificial intelligence (AI) and internet of things (IoT) applications. Next generation packaging technologies require tighter overlay to accommodate larger package sizes with fine-pitch chip interconnects on large-format flexible panels.

Do you have a Firefly G3 system question? Let’s talk!

As your partner for innovative solutions, we’re always here for you.

Discover how our cutting-edge semiconductor solutions are engineered to meet your most complex challenges: delivering performance, reliability and innovation where it matters most.

Let’s Talk

"*" indicates required fields

Dragonfly® G3 System

The Dragonfly G3 system is resetting the industry’s expectations for throughput, accuracy and reliability. Combining 2D and 3D technologies, the system detects yield-robbing defects and measures features critical for today’s semiconductor technologies

Product Overview

The Dragonfly G3 is a widely adopted pattern inspection system that utilizes line scan imaging technology to deliver fast, sub-micron defect detection for both R&D and high volume manufacturing environments. It features multiple illumination channels, including brightfield, darkfield, high-speed IR for embedded defects, and Clearfind® technology for detecting non-visual organic residues. Powered by modern machine learning algorithms, the Dragonfly G3 system offers a complete on-tool solution for defect detection, nuisance reduction and classification.

The system offers additional flexibility through the integration of multiple 3D metrology capabilities, including film thickness and structural profiling, and substrate thickness measurement. It features the latest 3Di™ technology, delivering and precise bump height metrology. The Dragonfly G3 system, with optional edge and backside inspection via the EB40 module, offers a comprehensive all-surface inspection solution for both front-end and back-end OQA.

Applications

- Redistribution layers (RDL): after develop, after etch

- Reconstructed and bonded wafers

- Micro bumps and Cu pillars

- Post saw

- Gel and waffle pack inspection

- Post probe and testing

- OQA

Featured Markets

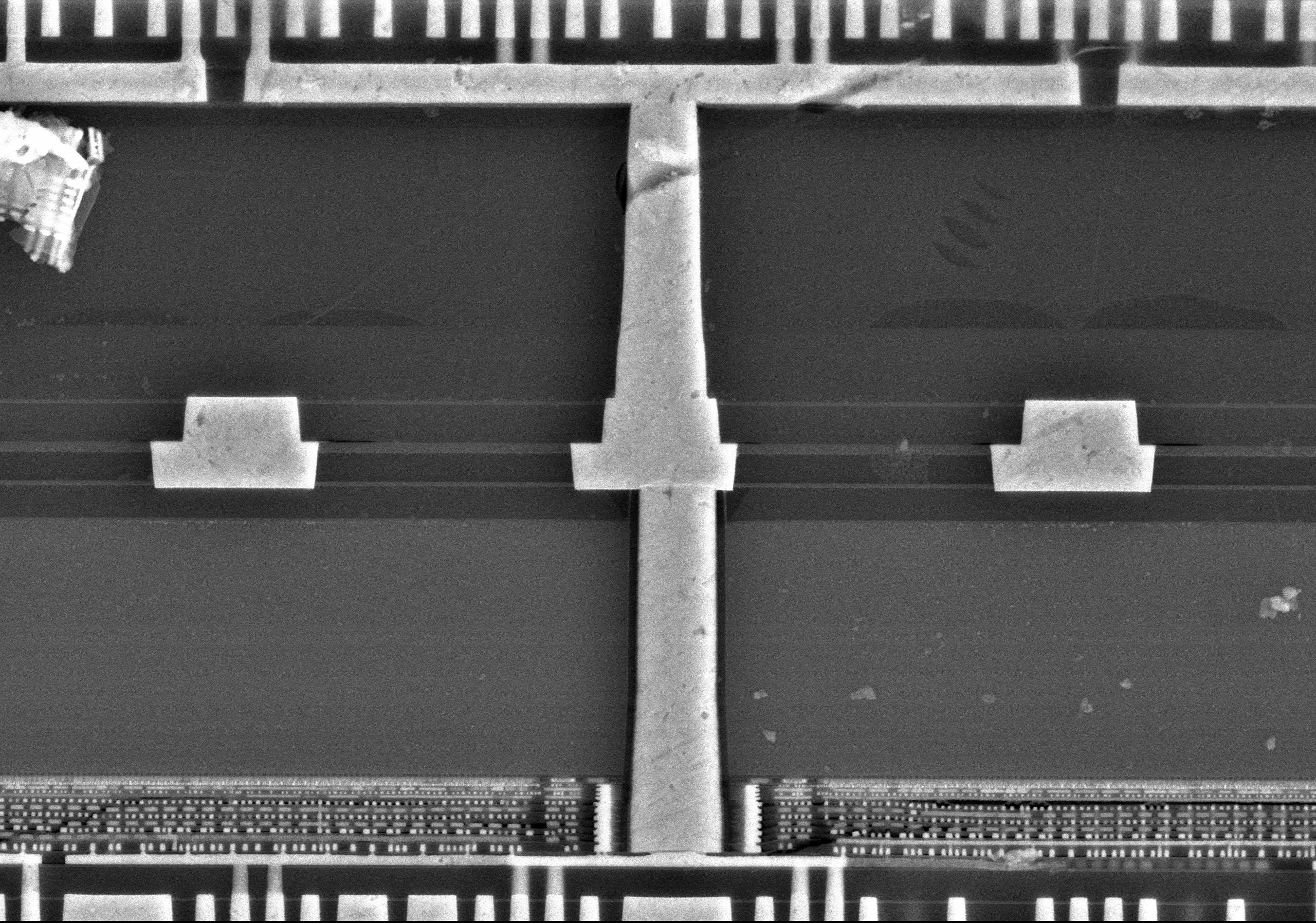

Hybrid Bonding Process Control Solution

Hybrid bonding enables ultra-dense 3D memory interconnects with up to 1,000x more connections than microbumps. Achieving high yield requires stringent process control, including monitoring topography and detecting particles, cracks and voids. Measuring dishing in copper pads provides valuable insight into surface conditions. Together, these process control insights contribute to improved device reliability and performance.

Enabling In-Line Process Control for Hybrid Bonding Applications

As demand grows for high-performance computing (HPC) and AI-driven applications, manufacturers are turning to hybrid bonding to enable the ultra-dense 3D integration required for next-generation chip architectures. This advanced packaging technology presents significant process challenges. Surface preparation must be precisely controlled to eliminate particles, excess recess, and copper pad dishing, all of which can compromise bond quality. During pre-annealing, particle-induced gaps and wide bonding gaps can prevent proper wafer contact. Post-annealing, the formation of dielectric and metal voids introduces further risks to electrical performance and long-term reliability.

Do you have a Dragonfly G3 system question? Let’s talk!

As your partner for innovative solutions, we’re always here for you.

Discover how our cutting-edge semiconductor solutions are engineered to meet your most complex challenges: delivering performance, reliability and innovation where it matters most.

Let’s Talk

"*" indicates required fields

NovusEdge® G2 System

The NovusEdge G2 System offers fast, reliable edge, notch and backside inspection for 300mm unpatterned wafers, utilizing modular configurations.

Product Overview

The NovusEdge G2 System provides high sensitivity inspection for the edge and backside of unpatterned wafers for current and advanced nodes. Configurable modules on the same automation platform increase throughput while maintaining a small footprint for improved cost of ownership. The edge-gripping handling solution for both automation platform and the inspection modules provide desired cleanliness required for manufacturing. Optional high-sensitivity notch inspection can be added. Defects are automatically classified and binned at run time to reduce manual review.

Designed as a multipurpose inspection and sorting system for end of line outgoing quality inspection of 300mm unpatterned wafers, the system identifies, inspects and sorts wafers according to recipes.

The NovusEdge G2 system offers higher sensitivity than the previous generation, with sub-micron resolution and increased throughput by over 15%. User interaction is simplified, and the new electrical design consumes less power.

Applications

- In-process unpatterned wafer sorting (grading)

- Incoming wafer inspection

- Tool qualification and monitoring

Featured Markets

Do you have a NovusEdge G2 system question? Let’s talk!

As your partner for innovative solutions, we’re always here for you.

Discover how our cutting-edge semiconductor solutions are engineered to meet your most complex challenges: delivering performance, reliability and innovation where it matters most.

Let’s Talk

"*" indicates required fields

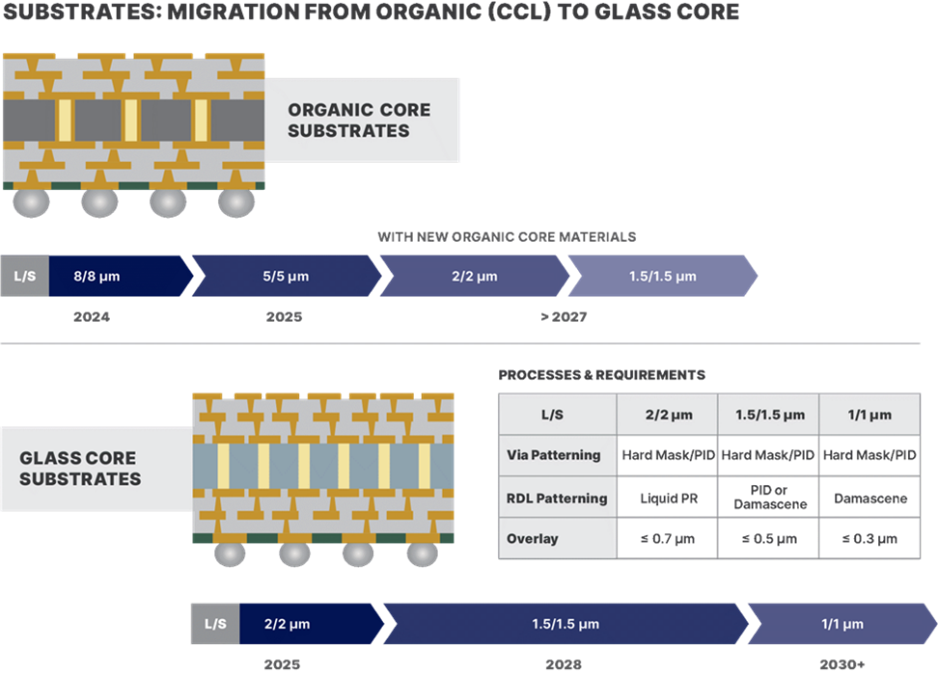

Onto Innovation’s Doug Brown is pleased to publish, “The Great Lithography Debate: Copper Clad Laminate or Glass Substrates?” in the January-February 2024 issue of the Chip Scale Review.

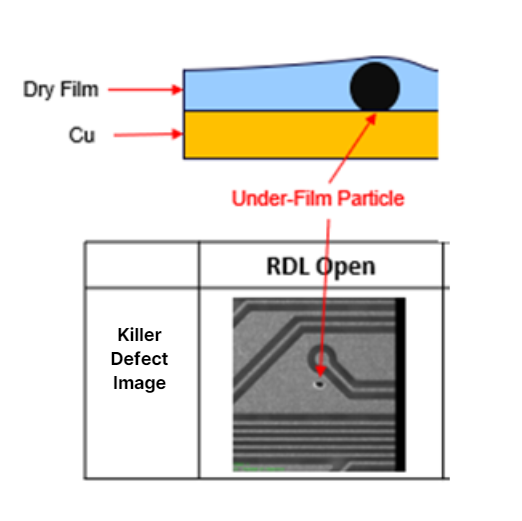

It is no mystery that the semiconductor industry is always advancing, with specifications becoming increasingly stringent as defects become increasingly more difficult to discover. This is especially true in the case of the most advanced nodes, where ever-smaller flaws and deformities can result in a killer defect.

To solve this More than Moore mystery, you do not need to employ the detective skills of Sherlock Holmes. You need the metaphorical equivalent of the pipe-smoking hero’s magnifying glass to find the particles, scratches, pits and air pockets hiding in the shadows.

Take the critical dimensions of trenches and vias, for example. As they shrink, the size of a particle or scratch that can potentially result in a killer defect decreases in size as well, making sensitivity an increased priority for bare wafer inspection — on the frontside and backside, at the edge and in the notch.

With an eye on evolving requirements for advanced node bare wafers, manufacturers are seeking inspection solutions with automatic defect classification (ADC) capabilities to perform outgoing quality assurance for wafers, including polished wafers and those with silicon epitaxial layers. Armed with these ADC capabilities, customers can significantly reduce the need for time-consuming and costly manual review.

The frontside, bulk, backside, edge and notch — each of these areas needs to be inspected to ensure the quality of the silicon wafer and the successful fabrication of advanced devices on the wafer. We’ll start with frontside and bulk before moving onto backside, edge and notch inspection, the main focus of this blog.