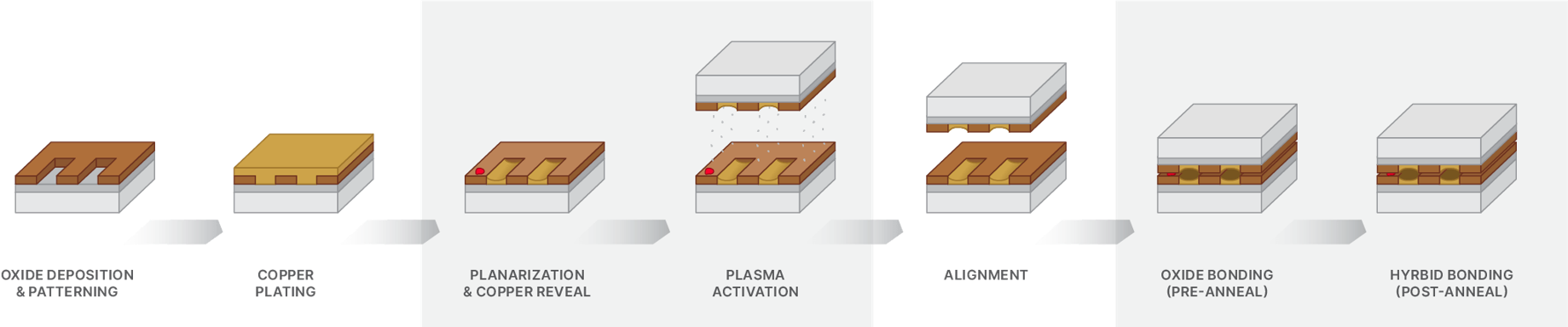

Enabling In-Line Process Control for Hybrid Bonding Applications

As demand grows for high-performance computing (HPC) and AI-driven applications, manufacturers are turning to hybrid bonding to enable the ultra-dense 3D integration required for next-generation chip architectures.

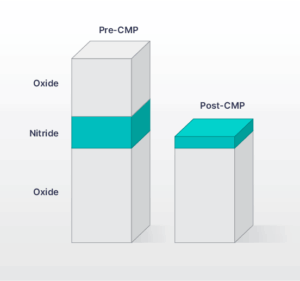

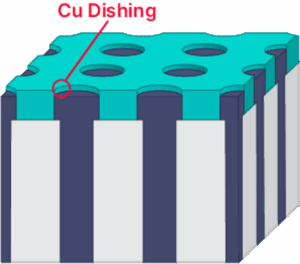

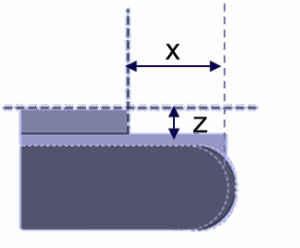

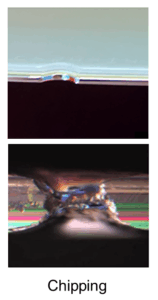

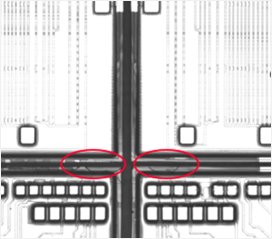

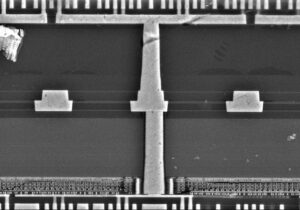

This advanced packaging technology presents significant process challenges. Surface preparation must be precisely controlled to eliminate particles, excess recess, and copper pad dishing, all of which can compromise bond quality. During pre-annealing, particle-induced gaps and wide bonding gaps can prevent proper wafer contact. Post-annealing, the formation of dielectric and metal voids introduces further risks to electrical performance and long-term reliability. If not carefully managed, these issues can lead to increased defectivity, reduced yield, and degraded performance in HPC and AI systems where reliability and speed are critical.

Source: AMD 3D V-Cache with TSMC SoIC 3D Packaging reverse engineering & costing report, Yole Group, 2022

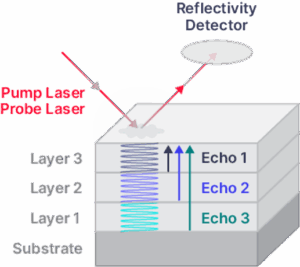

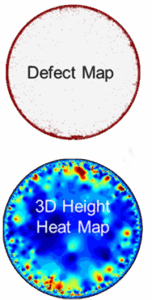

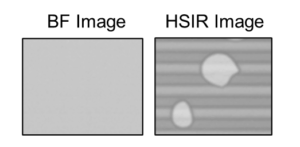

Hybrid bonding reliability starts with robust process control. Monitoring topography and detecting particles, cracks, and voids help identify defects early. Measuring copper pad dishing offers insight into surface conditions and planarity. Tight control during pre-bonding steps enables potential rework before permanent defects occur.

The following examples highlight key metrology and inspection techniques that support more consistent hybrid bonding outcomes.