From the cars we drive to the devices we hold and the medical systems that safeguard our health, bipolar-CMOS-DMOS (BCD) technology is at the heart of many modern electronics.

Today’s vehicles are packed with electronics like power engine management, anti-lock braking systems (ABS), airbag controllers, and electric vehicle (EV) charging infrastructure, each one demanding a seamless integration of analog, digital, and power functions. In the case of smartphones, audio amplifiers, and smart home devices, BCD devices help balance power efficiency with high performance. Meanwhile, medical imaging systems, such as ultrasound, and advanced power management solutions, rely on semiconductor technologies like BCD devices to handle diverse electrical requirements without compromising accuracy or safety.

Important as BCD devices may be, what exactly are they?

BCD devices are an advanced semiconductor process technology that integrates three distinct types of transistors—bipolar, CMOS, and DMOS—onto a single chip. The integration of these three transistors enables the simultaneous handling of analog, digital, and power functions within a compact and high-performance platform, with each transistor type contributing unique strengths:

- Bipolar transistors offer high current handling and precise analog control.

- CMOS transistors provide low power consumption and high integration density for digital logic.

- DMOS transistors are optimized for high-voltage and high-current power applications.

For BCD devices to meet performance expectations, proper process control measures are needed, especially in the case of silicon-chromium (SiCr) thin films.

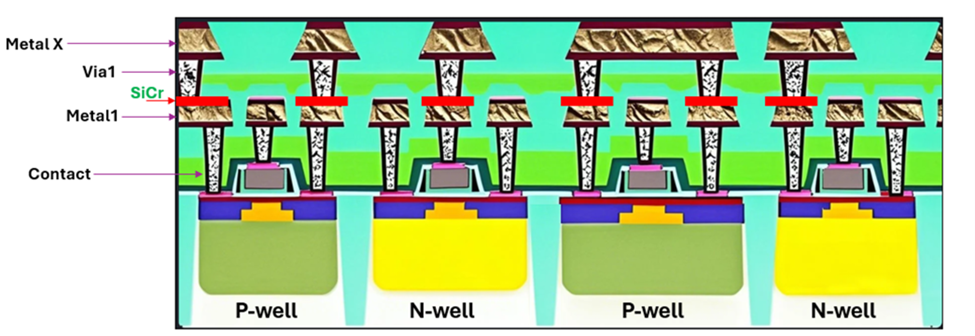

SiCr films play a critical role in BCD technology, primarily as precision resistive elements within analog and power management circuits (Figure 1.). SiCr resistors offer high stability, low temperature coefficient resistance (TCR), and excellent linearity, making them ideal for applications requiring accurate voltage and current control. Given the stringent reliability standards for BCD technology as demanded by the automotive industry and others, SiCr deposition must exhibit high reproducibility and minimal defectivity to support high-yield manufacturing and robust device performance under thermal and electrical stress.

Figure 1. Schematic of the BCD process, with SiCr film identified.

Uniformity across the wafer and repeatability between lots are critical. After all, minor thickness or compositional variations can lead to resistance drift which impacts analog accuracy and long-term reliability. Tight process control during the deposition step—including chamber stability, target conditioning, and plasma uniformity—ensures consistent film morphology and stoichiometry.

During SiCr sputtering, the precise regulation of specialty gas flow, in particular reactive gases such as nitrogen or oxygen, is critical, as their partial pressures influence plasma chemistry and the kinetics of silicide formation on the substrate. This silicide layer governs nucleation and grain growth, which directly affects grain boundary spacing and, consequently, TCR. Variations in gas flow can alter the stoichiometry and microstructure of the SiCr film, leading to shifts in TCR behavior, including the onset of a pronounced negative coefficient if the process is not tightly controlled.

Given the importance of these demands, manufacturers need the right tools on hand to maintain proper process control and optimize the performances of their BCD devices. In this article we will discuss the application of picosecond ultrasonic technology in two parts: one as a robust thickness metrology solution for qualifying SiCr deposition process and the second for excursion monitoring in BCD devices.

About Picosecond Ultrasonic Technology

Picosecond ultrasonic technology (PULSE™ technology) is a non-contact, non-destructive pump-probe laser acoustic technique for the measurement of metal film thickness. It is a proven workhorse in semiconductor fabs around the world. A 0.1ps laser pulse (pump) is focused to a small (~ 8´10mm2) spot onto a wafer surface to create a sharp acoustic wave. The acoustic wave travels away from the surface through the film at the speed of sound. At the interface with another material, a portion of the acoustic wave is reflected and comes back to the surface while the rest is transmitted. The probe pulse detects this reflected acoustic wave as it reaches the wafer surface. One can detect the change of optical reflectivity that is caused by the strain of the acoustic wave or alternatively detect, using a position sensitive detector (PSD), the deflection of the reflected probe beam that is caused by the deformation of the surface due to the acoustic wave. Both modes, reflectivity (REF) and PSD, are used in characterizing metal films. Knowing the speed of sound in the material, and the arrival time of the echoes, thickness is readily extracted using the first principles technique.

Film Thickness

With background on picosecond ultrasonic technology out of the way, we will turn our attention to the application of this technology as a robust thickness metrology solution for qualifying SiCr deposition process in BCD devices. To demonstrate this, we measured the nominal thickness of SiCr thin films using picosecond ultrasonic technology.

Figure 2a shows the raw data from the SiCr thin film. The acoustic echoes identified in the figure are used to calculate the thickness of the film using the speed of sound and round-trip transit time through the film. Nominally, textbook values for the longitudinal speed of sound would be used. In the case of SiCr films, the longitudinal speed of sound will vary from the bulk material and depend on the deposition process (sputtering, evaporation, etc.) and specific film composition (stoichiometry, density, etc.).

As a one-time calibration, we used cross-section transmission electron microscopy (TEM) to obtain SiCr film thickness and calculated the speed of sound for this specific process to be 69.7Å/ps. The modeled fit to the measurement is shown in Figure 2b.

Figure 2a. Raw data of reflectivity change vs time shown. The cross-wafer variation is identified by the shift in acoustic echoes.

Figure 2b. Modeled fit to measured data shown. The green curve represents the measurement, and the black curve represents the fit.

In Figure 3a, raw data from the DOE skew is shown. The shift in echo position between the different wafers demonstrates the sensitivity of the technique for monitoring the process. Within wafer uniformity profiles from 13 points across the wafer show consistent trends (Figure 3b).

Given the critical function of SiCr films in BCD device architecture, it is imperative to maintain highly uniform deposition with stringent process control to meet electrical and reliability specifications. Yield optimization is directly correlated with film uniformity as variations can significantly degrade device performance and long-term stability. As part of chamber qualification, more extensive sampling across the wafer, including to the edge, was performed (Figure 4). Those profiles are also consistent across the thickness skew.

Figure 3a. Raw data from the DOE thickness skew. Delta represents the skew in thickness from the target. The shift in echo position demonstrates the sensitivity for process monitoring

Figure 3b. Consistent cross wafer uniformity profiles for the three wafers.

Repeatability is a key metric in SiCr thin film metrology for ensuring robust process control and consistent device performance. Poor repeatability can obscure true process shifts, leading to incorrect corrective actions and potential yield loss. Gage capable repeatability measurements ensure compliance with automotive industry standards and are critical for long-term reliability. The dynamic repeatability data indicates performance is better than 0.5Å (1σ) and is more than sufficient to meet the process monitoring needs.

Figure 4. Forty-nine point wafer uniformity profiles for the three wafers, including measurements to the edge of the wafer. The profiles were consistent across the entire wafer.

As demonstrated, picosecond ultrasonic technology provides a precise, non-destructive method for measuring film thickness, validated against TEM calibration. The technique also offers exceptional repeatability and sensitivity, enabling manufacturers to monitor wafer-to-wafer and within-wafer uniformity with confidence. This capability is critical for maintaining tight process windows, as even minor deviations in thickness can lead to resistance drift and compromise analog precision. By integrating this metrology into chamber qualification and process monitoring, fabs can ensure consistent SiCr deposition, optimize yield, and meet stringent reliability standards.

Film quality

In picosecond ultrasonic technology, acoustic echoes are used to calculateSiCr film thickness. However, simultaneously available probe reflectivity data can be leveraged to provide information that can be used for process optimization (i.e., gas flow) and flagging process excursions. As such, this technique can be used to monitor the surface reflectivity of SiCr films; this application serves as a qualitative indicator of the film morphology and surface roughness and can be used for process control.

Figure 5. Surface reflectivity comparison for films having same target thickness but different reflectivity. Average reflectivity variation (top) across wafer is much higher than the thickness variation (bottom). Orange represents the lower flow rate, and blue represents the higher flow rate.

During the sputtering of SiCr films, gas flow has a strong influence on TCR as it impacts the film’s microstructure and stoichiometry (density and composition). This, in turn, determines the film’s stability, stress, and electromigration resistance in BCD applications. Uneven gas distribution causes local variations in thickness and composition leading to resistor mismatches and unpredictable TCR.

The surface reflectivity of the target wafer at two different gas flow rates is shown in Figure 5. Reflectivity data was collected at the same time as the acoustic data and shows the variation in surface reflectivity. At gas flow rate (b), the surface was more reflective corresponding to a smooth, dense film, whereas at flow rate (a), the reduced reflectivity indicates increased surface roughness which can degrade resistor uniformity and TCR stability.

Also, the thickness variation SiCr film is thinner at the higher N2 flow. N2 is known to affect silicide/nitride formation, grain spacing, etc., and impact both thickness and reflectivity. Studies are underway to characterize the impact of annealing temperature. The results are promising.

In summary, the surface quality of SiCr films plays an equally critical role in device stability and long-term performance. The study highlights how reflectivity measurements, captured alongside thickness data using the same picosecond ultrasonic platform, serve as a powerful indicator of film morphology and density. Variations in gas flow during sputtering were shown to significantly influence both reflectivity and thickness, underscoring the importance of precise control over deposition parameters. A smoother, more reflective surface correlates with improved resistor uniformity and predictable TCR behavior, while rougher films can degrade electrical performance.

Based on these results, we have demonstrated that reflectivity measurements, along with thickness measurements, can be leveraged for in-line monitoring to detect deviations in deposition parameters. By leveraging dual metrics—thickness and reflectivity—manufacturers gain a comprehensive, in-line process control solution that enables early detection of excursions and proactive corrections, ensuring robust SiCr thin film integration in advanced BCD architectures.

Conclusion

From automotive safety systems to medical imaging and consumer electronics, BCD technology enables the seamless integration of analog, digital, and power functions that modern applications demand. Yet, this versatility hinges on precise control of SiCr thin films whose stability and uniformity directly influence device reliability

Achieving this level of integration comes with significant manufacturing challenges, particularly in controlling SiCr film thickness and gas flow during sputtering, factors which directly impact resistor stability and temperature performance, which are critical for reliability in demanding environments. To overcome these hurdles, we propose using picosecond ultrasonic technology.

With picosecond ultrasonic technology, manufacturers have a powerful, non-destructive tool for monitoring thickness and reflectivity at the ready, one that ensures that SiCr films meets stringent performance standards. In doing so, manufacturers will be able to safeguard the integrity of BCD devices while supporting the continued evolution of new technologies across the automotive, medical, and consumer electronics sectors.

By Huayuan Li, Alex Hong, Johnny Mu, Timothy Kryman, and Priya Mukundhan

You Have a Challenge? Let’s talk.

We’d love to connect with you.

Looking to learn more about our innovative solutions and capabilities? Our team of experts is ready to assist you. Reach out today and let’s starts a conversation about how we can help you achieve your goals.

Let’s Talk

"*" indicates required fields

Abstract

Picosecond Ultrasonics (PULSE™) Technology has emerged as a leading metrology solution for characterizing single-layer and multilayer metal films in advanced semiconductor manufacturing [1]. As a non-contact, non-destructive technique, PULSE Technology has become the tool-of-record across multiple device segments, including logic, radio frequency (RF), memory, microelectromechanical systems (MEMS), and flash memory. Its ability to measure both film thickness and elastic modulus [2,3] in-line makes it indispensable for process control and material characterization.

Backside metallization (BSM) is essential in semiconductor fabrication, particularly for power electronics, logic ICs, and advanced memory devices. It involves depositing metal layers on the wafer’s reverse side to improve electrical conductivity, thermal dissipation, and mechanical stability. As device architecture becomes more complex, precise control and measurement of BSM layers are critical for ensuring performance and reliability. Driven by demand from semiconductors, photovoltaic, MEMS, and LED sectors, the BSM market is expanding rapidly [4]. Technologies such as PVD, CVD, electroplating, and sputtering enable tailored metal stacks, but they also pose metrology challenges—especially for non-destructive, multilayer characterization. These metal layers typically range from 50 nm to 3 µm in thickness, with total stack thicknesses reaching up to 5 µm.

Accurate characterization of BSM layers is essential for ensuring device reliability, performance, and manufacturing yield. Traditional metrology techniques such as scanning electron microscopy (SEM), atomic force microscopy (AFM), four-point probe, X-ray reflectometry (XRR), and X-ray fluorescence (XRF) often face limitations in throughput, destructiveness, thickness limitations, or sensitivity to surface roughness. In contrast, Picosecond Ultrasonics offers a compelling alternative, providing high-precision measurements across a wide thickness range with micron-scale spatial resolution. Its ability to simultaneously resolve multiple layers in a single measurement, even on rough or non-planar surfaces, makes it particularly well-suited for BSM applications.

In this paper, we demonstrate the application of Picosecond Ultrasonics to backside metallization metrology. We present data showing its capability to measure both single-layer and multilayer metal stacks with excellent repeatability, long-term stability, and high throughput. The technology’s small spot size—on the order of microns—enables measurements on small pads as small as 15 µm, improving spatial resolution and enabling in-line monitoring on product wafers. Furthermore, advanced features such as dual modulation, crossed polarization, and adaptive measurement controls enhance performance on challenging surfaces, including aluminum and complex BSM stacks.

You Have a Challenge? Let’s talk.

We’d love to connect with you.

Looking to learn more about our innovative solutions and capabilities? Our team of experts is ready to assist you. Reach out today and let’s starts a conversation about how we can help you achieve your goals.

Let’s Talk

"*" indicates required fields

Mid-infrared ellipsometry offers a powerful approach for non-destructive optical critical dimension (OCD) metrology in advanced semiconductor manufacturing. This technique supports in-line measurements of high aspect ratio structures, such as those found in 3D NAND memory devices. The incorporation of quantum cascade lasers and fast phase modulation allows rapid acquisition of Mueller matrix elements with high spatial resolution and sub- Å precision. Material-specific absorption in the mid-infrared range allows depth-resolved profiling of device structures, overcoming the limitations of conventional OCD. Rigorous coupled wave analysis is used to extract structural parameters from the measured spectra. Agreement with destructive reference metrology has been demonstrated on a variety of structures. The ability to measure multiple Mueller elements further enhances characterization of complex geometries, making mid-infrared ellipsometry a valuable tool for process control in semiconductor fabrication.

This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. This article appeared in Journal of Applied Physics (Vol.139, Issue 7) and may be found at https://doi.org/10.1063/5.0310009

DOI: 10.1063/5.0310009

You Have a Challenge? Let’s talk.

We’d love to connect with you.

Looking to learn more about our innovative solutions and capabilities? Our team of experts is ready to assist you. Reach out today and let’s starts a conversation about how we can help you achieve your goals.

Let’s Talk

"*" indicates required fields

As artificial intelligence (AI), high-performance computing (HPC), and advanced graphics processing continue to push the limits of memory throughput, the demand for high-bandwidth memory (HBM) has surged. These applications require faster access to massive datasets, driving the need for memory solutions that can deliver both speed and density without compromising power efficiency. HBM addresses this by stacking memory dies vertically and connecting them with ultra-fast interconnects. However, as data rates climb, traditional bump technologies—long relied upon as the primary interconnect method—are reaching their physical and performance limits.

Today, we stand at a pivotal moment in HBM interconnect technology. Hybrid bonding has emerged as one of the most talked-about technologies in advanced packaging. Promising finer pitches and superior electrical performance, hybrid bonding is generating excitement for its potential in high-performance applications. On the other hand, innovations in bump scaling are making bumps increasingly viable for a broad range of applications, beyond legacy and cost-sensitive applications. Despite these advancements, scaling bump pitch beyond 10μm and toward 2μm presents significant challenges. Maintaining uniformity and controlling bump height variation becomes more difficult, impacting yield and reliability. Meanwhile, taller HBM stacks, from 8-high to 24-high, require thinner dies, increasing the risk of die warpage and cracks during dicing.

Hybrid bonding is not without its challenges, too. At this scale, direct bonding demands plating uniformity and surface cleanliness to ensure reliable interconnects. In this article, we will examine the challenges facing bump and hybrid bonding technologies, the solutions these two technologies enable, and how they stack up compared to each other. We also will highlight how manufacturability, reliability, and process control evolve as pitches shrink and stack heights increase. To start with, we focus our attention on bumps, and then move on to hybrid bonding.

Bump metrology evolution

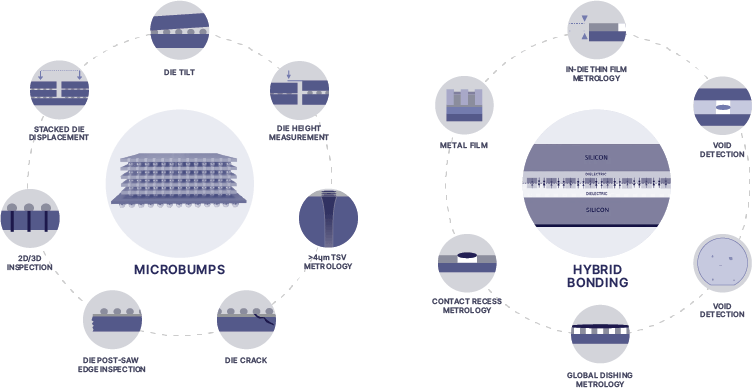

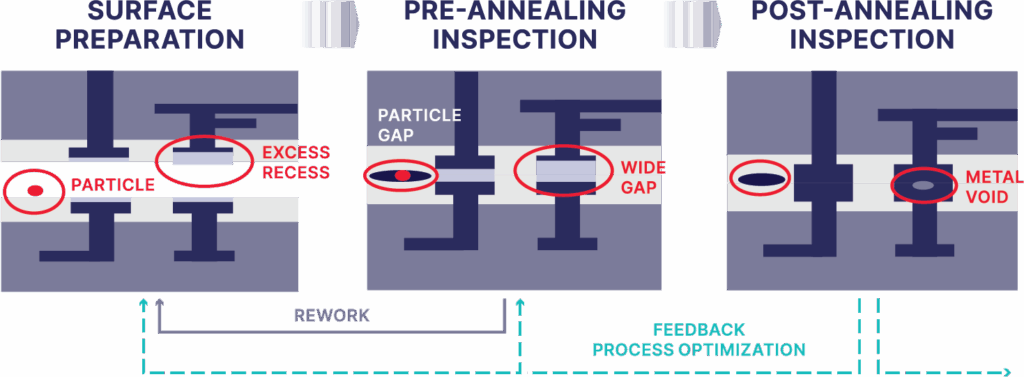

Microbumps play a critical role in enabling vertically-stacked HBM structures by serving as interconnects between dies, and dies to interposers or substrates. These bumps need to be uniform in height, properly aligned, and defect free (Figure 1).

Figure 1. Interconnect challenges in microbump and hybrid bonding technologies.

Inconsistent bump height in HBM can result from plating nonuniformity and process variability, and it negatively affects yield, reliability, and performance. Meanwhile, poor coplanarity can lead to mechanical stress, interconnect fatigue, or thermal cycling failures, while inconsistent contact can degrade signal integrity and power delivery. Misalignment during flip-chip bonding can result in open or short circuits. Given the breadth of these challenges, manufacturers should focus on identifying issues after the plating step and before the reflow step. After all, if you have a plating problem but move onto reflow, it will be too late to fix the problem.

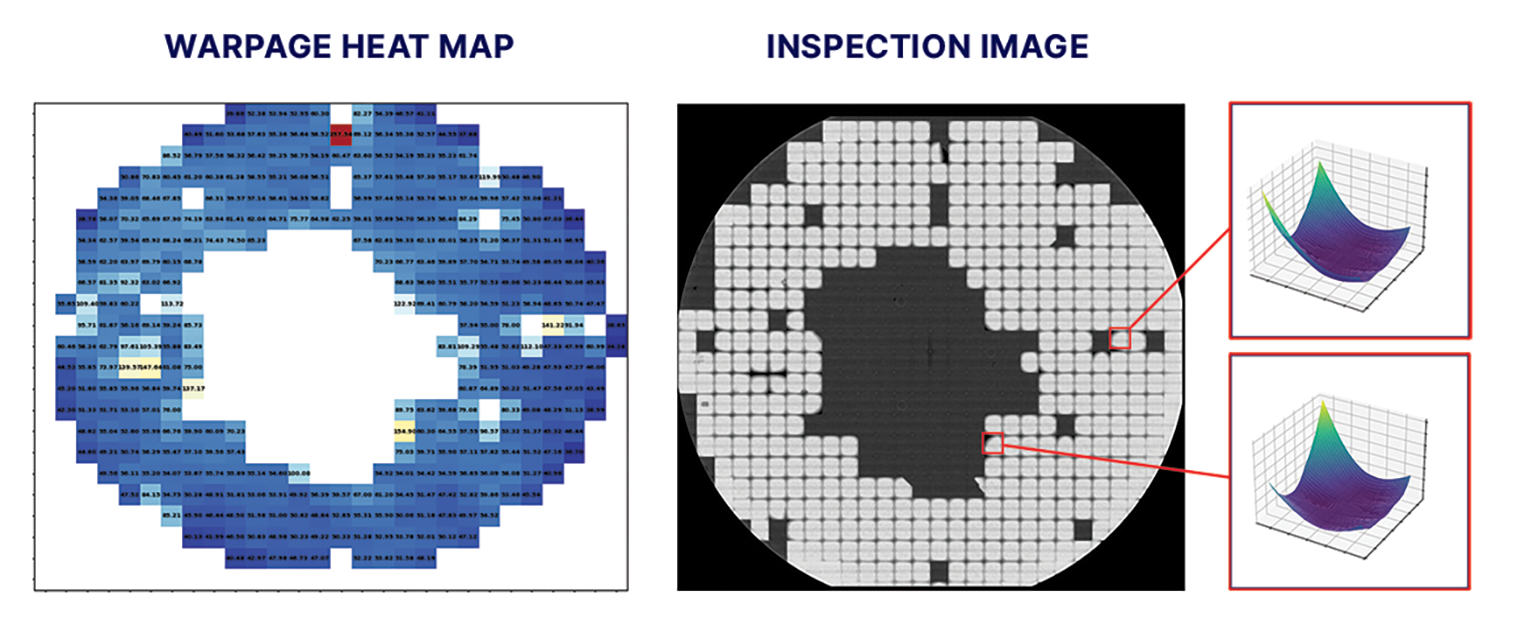

With the number of layers in an HBM stack continuing to rise, addressing die warpage becomes even more essential (Figure 2). First of all, die warpage significantly compromises stack alignment and bonding quality. This is especially critical given the extremely tight tolerances of HBM. In addition, warpage can also result in voids, opens, and a host of other issues leading to electrical failures, mechanical stress and cracking, yield loss, and thermal performance degradation, resulting in overheating and reduced performance. Meanwhile, organic residue can result in surface contamination, voids and delamination, oxidation and corrosion, and diminished yield and reliability.

Properly identifying cracks and alignment errors in bumps poses another challenge (Figure 3). Cracks often occur during the dicing and backside grinding process and can break the electrical path, leading to open circuits. They often propagate due to thermal cycling, especially in materials with different coefficients of thermal expansion (CTE), weakening the bump structure. Even if initially functional, cracked bumps are prone to failure under thermal or mechanical stress during operation.

Misalignment of dies is another problem. It is often caused during the pick and place step due to the lack of backside patterns. This lack of patterning makes it difficult to tell if overlay is accurate—this is something with which automated optical inspection systems struggle.

Rise of hybrid bonding

The key reason hybrid bonding has emerged as a new technology for HBM is simple: improved interconnect density and smaller package sizes. To begin with, hybrid bonding enables finer interconnect pitches, less than 10μm, allowing for more I/O terminals in a smaller area. This increased density translates directly into higher bandwidth and improved overall performance.

Traditional bump-based stacking introduces gaps of about 30μm between dies. Hybrid bonding offers direct Cu-to-Cu connections, thereby achieving near-zero spacing between dies, significantly reducing overall package thickness and offering lower resistance and better thermal conductivity than bump-based methods. This improves signal integrity, reduces power consumption, and enhances heat dissipation, all of which are critical for HBM.

Finally, hybrid bonding supports several configurations: wafer-to-wafer, die-to-wafer, and die-to-die, offering flexibility in manufacturing and integration. This adaptability is vital for scaling HBM technologies across different applications and performance tiers.

With our introduction to bumps and hybrid bonding complete, we now turn to a comparative discussion of these two technologies, building on earlier points and exploring new ones.

Bump vs. hybrid bonding

Bumps have several advantages over hybrid bonding. As a mature technology, they are widely used and well understood in the industry, are compatible with existing flip-chip and underfill processes, and are scalable for moderate density. The cost of bump technologies is lower than hybrid bonding technologies. Bumps, however, have a number of disadvantages compared to hybrid bonding. The most significant of which are the pitch limitations of bump technologies, which struggle at pitches below 10µm due to challenges in plating uniformity and solder reflow. Bumps also require underfill, which can introduce stress and complicate thermal management.

Despite the limitations noted above, bump technology continues to evolve. Leading suppliers of bump plating systems project a continued downscaling of bump dimensions, with diameters decreasing to the 4µm-5µm range and heights dropping as low as 1µm to 2µm. At a 10µm pitch, the lateral footprint remains sufficient to support the high-density I/O requirements of advanced memory architectures. Concurrently, the reduced bump height enables vertical integration of up to 16 stacked HBM dies within the 775µm maximum package height defined by Joint Electron Device Engineering Council (JEDEC) standards. Consequently, bump interconnects remain a viable and scalable solution for next-generation HBM, and major manufacturers are maintaining substantial R&D investments in bump technology.

Hybrid bonding, while promising, presents its own set of challenges. In addition to being more expensive than traditional bump technologies, hybrid bonding may require manufacturers switching from bump technology to purchase new equipment and adopt new process flows. In addition, hybrid bonding is especially sensitive to particles and organic residues; for example, even 1µm particles can cause defects. Such residues can prevent proper contact, trap gases or moisture, and lead to void formation during bonding. These voids can cause delamination or incomplete bonding, reducing mechanical integrity and electrical continuity.

Interconnect solutions

Process control for hybrid bonding is challenging, but these obstacles can be addressed by employing a suite of advanced metrology and inspection technologies, as well as analytic software solutions.

High-speed, sub-micron inspection can be used to detect surface anomalies such as particles, residues, and backside and edge defects (Figure 4). This ensures that bonding surfaces are clean and defect-free before the bonding process begins. As for overlay misalignment, the capability to measure wafer topography and alignment with sub-micron precision enables accurate die placement and reduces the risk of misalignment during bonding. As for voids, a non-contact, immersion-free acoustic metrology technology capable of detecting voids down to 1µm is effective at identifying bonding defects that could lead to electrical or thermal failures. Furthermore, a sub-micron inspection system can be used to detect defects like cracks and delamination caused by thermal or mechanical stress.

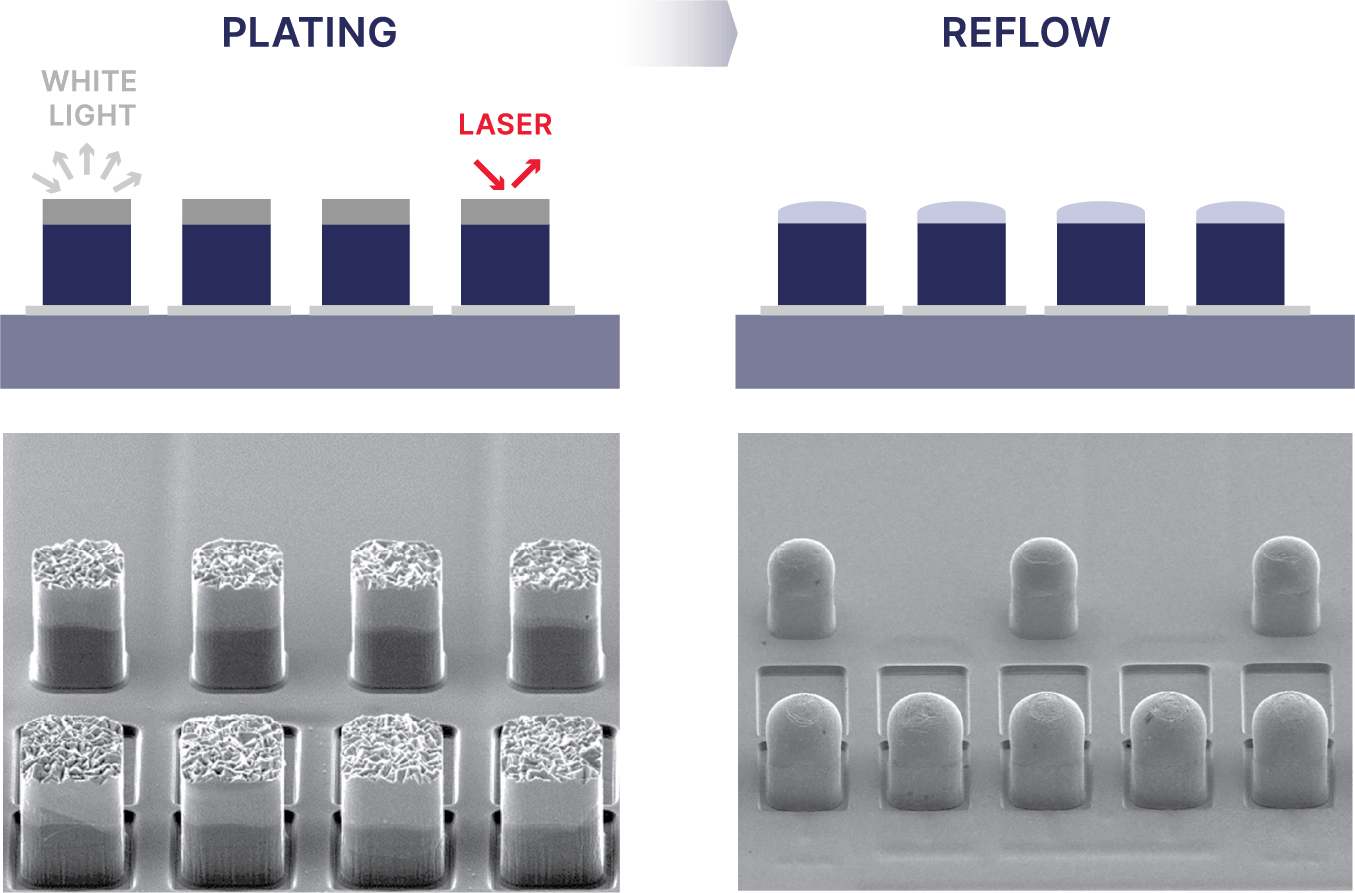

Figure 4: Hybrid bonding metrology and inspection challenges.

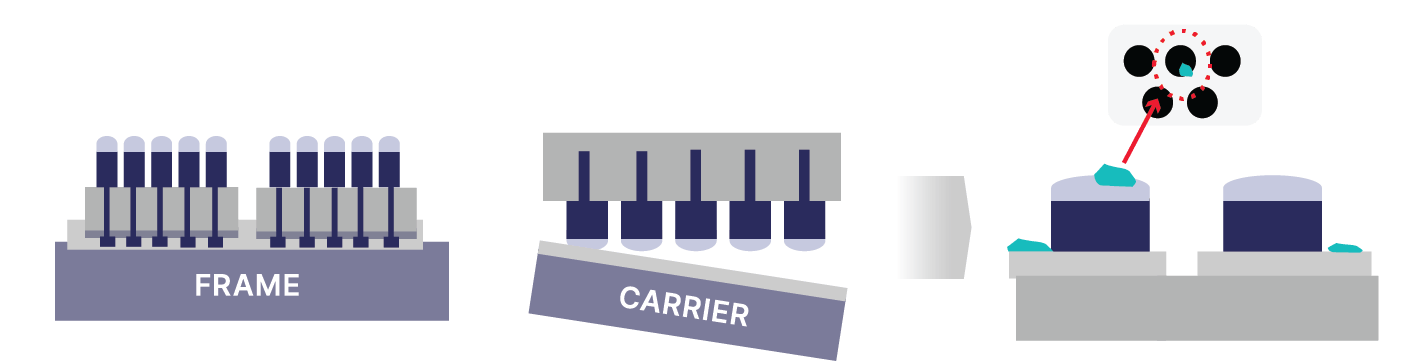

In the case of bump-based interconnects, the ability to measure Cu-to-Cu bump height down to 1.5μm will be key. However, several of today’s technologies employ white light illumination technologies that are unable to properly identify defects on these exceptionally small Cu pillars before reflow (Figure 5). After reflow, the bump shape is very clean and very smooth; but before reflow and after plating, the Cu is very rough. Typically, when white light hits a very rough surface, the light randomly scatters. However, an inspection system that uses a coherent wavelength laser technology can overcome this challenge.

In addition to the points noted above, an integrated system using analytical software can be used to detect errors and provide real-time defect analysis and statistical process control. Software can be used to provide in-line process control insights about defects and offer actionable corrections and is capable of handling millions of bumps per wafer, with each bump generating multiple data points. This integration helps manufacturers trace contamination sources and optimize cleaning steps, improving bonding reliability.

Summary

New technologies are actively being adopted for interconnect control in HBM. In the case of bump process control, the sector is moving toward smaller dimensions, 12µm to 4µm in high-volume manufacturing and below 2µm in R&D. Meanwhile, hybrid bonding is gaining traction due to its ability to support higher interconnect density and performance. This shift is driving the adoption of advanced inspection and metrology techniques, including an opto-acoustic void detection technology capable of detecting voids down to 1µm—a critical point for yield in HBM production.

Foundries are integrating bump inspection and metrology tools into their advanced packaging lines, especially for custom HBM and logic solutions. At the same time, hybrid bonding adoption is accelerating, particularly in the case of chiplet-based and heterogeneous integration strategies.

This year, R&D is expected to push microbump pitch to 6µm and hybrid bonding density to 60 interconnects/mm². In the coming years, microbump pitch may scale down to 3µm, while hybrid bonding density could reach 100 interconnects/mm². Long term, hybrid bonding is projected to become a mainstream interconnect technology, surpassing microbumps in many advanced applications, with densities reaching 150 interconnects/mm² and microbump pitch shrinking to 1.5µm.

As it stands today, there is no single solution for all HBM use cases. Instead, manufacturers may adopt an approach leveraging both bump and hybrid bonding, supported by a comprehensive process control strategy that integrates metrology, inspection, and advanced analytics.

Biographies

Damon Tsai is the Senior Director of Product Marketing, Inspection, at Onto Innovation, Milpitas, California. He joined the company in 2018 and has extensive experience in inspection and metrology, with a specialized focus on semiconductor FEOL, advanced packaging, OSAT, and specialty markets like RF, Power, and CIS.

Woo Young Han is Product Marketing Director, Inspection, at Onto Innovation, Richardson, Texas. He joined Onto Innovation in 2000 and holds an Electrical Engineering degree from the University of Toronto.

You Have a Challenge? Let’s talk.

We’d love to connect with you.

Looking to learn more about our innovative solutions and capabilities? Our team of experts is ready to assist you. Reach out today and let’s starts a conversation about how we can help you achieve your goals.

Let’s Talk

"*" indicates required fields

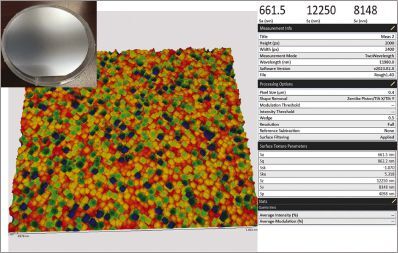

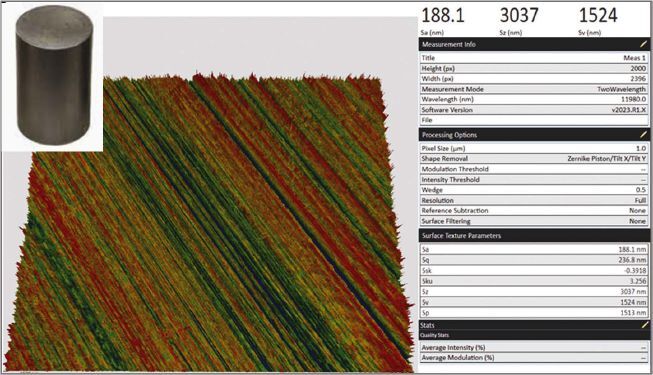

Optical measurement technology delivers nanometer resolution for real-time roughness analysis.

Surface roughness is the deviation of a surface from its ideal form. The larger the deviation, the rougher the surface. When using a 2D measurement technique, the roughness average is represented as Ra, while it is known as Sa when calculating roughness from 3D area measurements.

Most machined surfaces have an average roughness (Sa) of 200 nanometers (nm) to 2 µm (8 to 80 µin but can go down to less than 25nm. Traditionally, surface roughness has been measured using either subjective visual tests or two-dimensional (2D) stylus tools. For aerospace components, deviations from surface roughness specifications can cause performance issues such as increased wear, fracturing, disrupted fluid or air flow, poor adhesion of coatings and lubricants, and reduced corrosion resistance.

While visual testing techniques are inexpensive and easy to use, they do not deliver quantitative results. They cannot meet the gage repeatability standards many aerospace manufacturers require.

Using a 2D stylus offers quantifiable results, but faces hurdles in meeting gage repeatability standards, especially on the shop floor. The 2D stylus offers only a single trace with limited data points, and the results are directionally dependent-based on whether the scan is performed horizontally, vertically, or at an angle across the sample surface. Measuring corners and odd angles adds further challenges. The resolution of a 2D stylus system also depends on the size of the stylus tip.

Additionally, a 2D stylus is a contact-based tool. It can be damaged when measuring parts, especially at the edges, and can potentially damage the part itself.

Traditional quality control lab 3D optical profilers offer many advantages over 2D tools, including higher resolution, a larger measurement area of 3D data, and a true 3D Sa value. But they are limited by long turnaround times and the need to replicate large parts that do not fit under the microscope. They are also vibration-sensitive and require stable platforms, making them impractical for shop-floors.

The 4Di InSpec SR, addresses these challenges with a portable 3D surface gauge that delivers microscope-quality nanometer resolution measurements in real time. With a field of view of 1mm x 0.8mm, the measurement system acquires millions of data points in a single area, with a roughness accuracy of u0026lt;0.5%, and can measure machined surfaces from mirror-smooth to sandpaper-rough.rnrnThe system enables in situ surface finish and roughness measurements below 25 nanometers in seconds, while meeting gage repeatability standards. Machinists can achieve surface finishes at very small scales, creating performance improvements whether the part is a turbine blade or rivet on a wing.

The 4Di InSpec SR measures roughness on large components without the need for replication by bringing the system directly to the part. Its scratch-free optical technology eliminates surface damage concerns. The system employs vibration-immune technology, enabling fast quantification of surface roughness for both smooth and rough components on the shop floor.

A significant capability of the 4Di InSpec SR is its robot compatibility for automated measurements. Looking to the future, there are numerous opportunities to extend its benefits in shop floor applications, including automation integration, multi-sensor systems for macro and micro level measurements, and advanced predictive analytics capabilities.

The 4Di InSpec SR represents a significant advancement in quality control technology, offering aerospace manufacturers a unique real-time, shop floor surface measurement solution that bridges the gap between traditional laboratory precision and production-line practicality.

By Cheolkyu Kim, Onto Innovation, and Dae-Seo Park, Samsung Electronics Co., Ltd.

Picosecond ultrasonic technology can provide a metrology solution with excellent accuracy and gage capability for the control of interconnect processes in advanced packaging.

Looking back, 2024 will likely be remembered as a turning point for artificial intelligence (AI). Thanks to the spread of ChatGPT, Microsoft’s Copilot and other large language models, as well as various generative AI tools for video and images, AI has emerged as a tool used by millions of people every day. To create these new high performance AI devices, memory and process chips are packaged together to enable faster communication and lower power consumption. Such devices use advanced packaging technologies like heterogeneously integrated 2.5D and 3D structures.

In these 2.5D and 3D structures, conventional memory chips are replaced with high bandwidth memory (HBM) and paired with a graphics processing unit (GPU). The HBM enables the higher data transfer rates needed to handle the significantly increased data processing generated by parallel computation with the GPU. In the latest generation HBM, eight to 12 DRAM chips are connected to each other vertically by through silicon vias (TSV) to form one HBM package. Then four to six HBM packages are connected, horizontally, with the GPU chip by redistribution layers (RDL) on a Si interposer. These new interconnected structures offer significantly improved computing power, latency and higher bandwidth for data transfer and low power consumption as required by AI computing.

In the case of RDL on a Si interposer, manufacturing multiple layers of RDL is required to handle high data transfer rates. As such, the manufacturing process is much more complex compared to the manufacturing process for more mature packages. Metals, mostly Cu, in RDL are typically deposited using the electroplating (EP) process. The thickness of the metals is affected by the geometric structure underneath, making thickness uniformity control very challenging. To meet the within wafer uniformity requirement for RDL impedance control, measuring and monitoring metal thickness directly on product wafers is crucial. As RDL lines shrink to 2µm or lower – the line/space (L/S) requirements of the most advanced packages – dimensional control is vital to device performance while process control itself becomes even more stringent.

After the final RDL layer on a Si interposer is formed, bonding pads are created. These bonding pads connect with HBM or GPU chips through micro-bumps. Like RDL, bonding pads are also created using the EP process. However, some bonding pads are flat while others possess a dimpled structure. To maintain process control, engineers will still need to measure metal thickness directly on both flat and dimpled structures. In the case of the latter, such measurements are a lot more challenging. To meet these requirements for RDL and bond pad process control, tools enabling in-line metrology on less than 10μm sites are needed. As such, this process requires front-end style process control, with in-line metrology capabilities on a very small site with a very tight process control window.

Picosecond ultrasonic technology has been well adopted in front-end process control, and it can help AP houses better control metal thickness and wafer uniformity to meet device performance expectations. Before we get to that discussion, we will briefly review the traditional packaging process.

Traditional Packaging Process

During the traditional packaging process, metal film measurements are characterized using automated and semi-automated measurement tools such as X-ray fluorescence or sheet resistance measurements. These tools are easy to use and offer low cost of ownership. However, X-ray fluorescence or sheet resistance measurements are not up to the task of measuring multi-layered films or films with varying topographies on product wafers in high volume manufacturing.

Several commercially available white light scanning interferometer (WLSI) systems are also used in RDL process monitoring. These methods rely on wavelength-dependent interference patterns to provide the step height of metals; this assumes that the step height is the same as metal thickness, which may or may not be true depending on the structure.

As RDL films become thinner, wavelength dependent interference patterns become less sensitive to thickness variation. This affects measurement accuracy. In the case of RDL lines 2µm L/S and lower, the accuracy of thickness measurements becomes even more critical for process monitoring and control. However, WLSI systems have shown limitations in meeting these metrology requirements.

In general, the front-end process must operate inside a window that varies within 10% of the target value. This, in turn, requires a metrology tool with a gage capability (3σ repeatability and reproducibility) of 10% of the variability or 1% of the target value. This metrology tool must be able to measure in-die areas and on test structures smaller than 50µm on real product wafers. Such a tool also needs to be non-contact, non-destructive and fast enough to support high volume production. Picosecond ultrasonic technology enables advanced packaging manufacturers to meet these challenges.

As the AP process becomes more like the front-end process, metrology technology adopted in the front-end will need to be employed. In this article, we will show how picosecond ultrasonic technology can be used to measure metal films during RDL and bond pad processes.

About Picosecond Ultrasonic Technology

Picosecond ultrasonic technology is a non-contact, non-destructive pump-probe laser acoustic technique used to measure film thickness. This technology measures the round-trip travel time of ultrasonic acoustic waves within film. Using the speed of sound in the material, thickness can be readily extracted using a first-principles technique. Ultrasonic acoustic waves can be generated by a green laser pulse (pump) of 0.2 picoseconds (ps) width that is focused to approximately 8´10µm2. An acoustic wave generated by the pump pulse travels away from the surface through the film at the speed of sound. At the interface with other material, a portion of the acoustic wave is reflected and comes back to the surface while the rest is transmitted. The round-trip time of the acoustic wave can be measured using the time delay between the generation of the acoustic wave and the return of the reflected sound wave after interfacing with other material. The returning wave can be detected using another laser pulse (probe) that splits from the same laser source as the pump. The technique provides accurate measurement of both single-layer and multi-layer metal films.

There are two methods for detecting and measuring the arrival time of the returning sound wave to the surface. One way is to detect small changes in surface reflectivity caused by the density fluctuation of the returning acoustic wave; this is referred to as REF mode. The other way is to detect surface deformation using the returning acoustic wave. Surface deformation can be detected in position sensitive detector (PSD) mode. This consists of two detector cells that are aligned so that the probe beam hits the center of the two detector cells. When the acoustic wave reaches the surface, deformation causes changes in the direction of the reflected probe beam, resulting in a change to the difference between the intensities of the two detectors being measured.

In our study, we used fifth generation picosecond ultrasonic technology to measure the thickness of individual metals on multi-layer structures. This version of the technology features multiple improvements over previous generations. One of the most important improvements for metrology in advanced packaging involves measuring very rough film such as thick RDL.

To measure very rough film, pump beam intensity is modulated at 5 MHz. This modulates the intensity of the acoustic wave it generates. Then the reflected probe beam signal from the detector is demodulated with the same frequency as the pump modulation. This allows for the measurement of extremely weak reflectivity changes caused by the acoustic wave. As the pump beam itself does not convey any information about the travelling acoustic wave but has the same frequency as demodulation, demodulating the signal from the detector may include the signal from the pump. This results in significant noise, especially in the case of very rough films where pump beam scattering is very strong. Fortunately, such noise can be filtered out by further modulating the probe beam at a different frequency, 0.5MHz, and demodulating the signal from the detector with the sum of the two frequencies, 5.5 MHz.

Another significant improvement made to this technology is that the maximum probe beam time delay for the measurement has increased from 5 nanoseconds (ns) to 15ns. This means the maximum thickness that can be measured has increased threefold. For Cu measurement, the maximum thickness that can be measured is now 35μm.

Now that we have discussed picosecond ultrasonic technology, we will turn to our findings.

Measuring Films

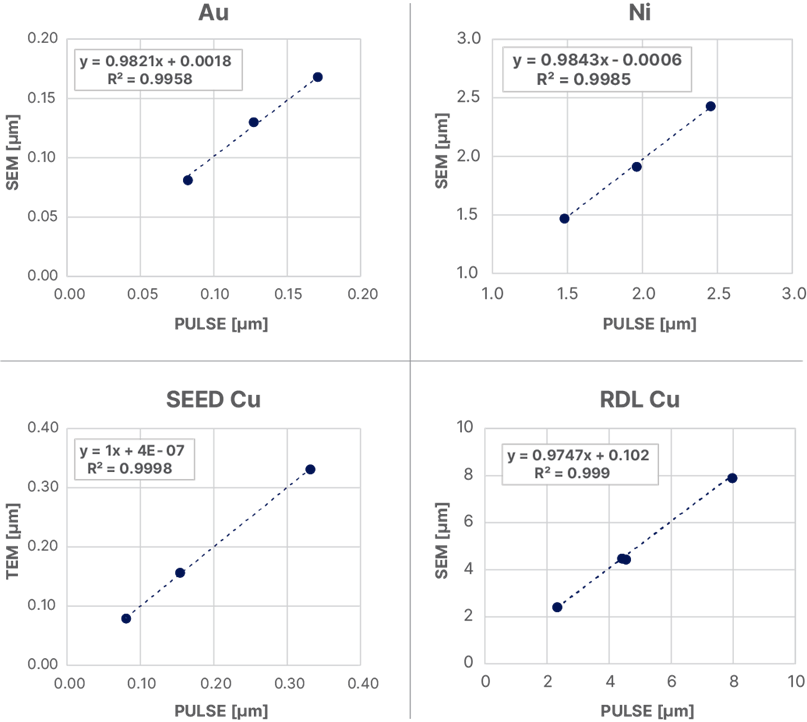

To start with, we conducted a test to confirm the accuracy of picosecond ultrasonic technology when measuring the films typically used in AP: Au, Ni, physical vapor deposition (PVD) seed Cu and RDL Cu (EP). For each film, we used picosecond ultrasonic technology to measure wafers of varying thicknesses. We then cut the wafers for cross-section analysis and estimated the correlation with the picosecond ultrasonic results. Fig. 1. shows the results for the four films. In this scenario, the correlation factor R2 was higher than 0.99 for all four cases, with the slope close to one, clearly demonstrating the accuracy of picosecond ultrasonic measurements.

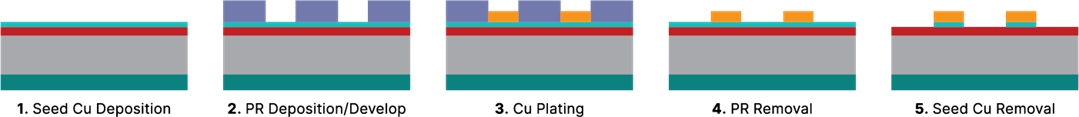

Following this, we measured product wafers in various interconnect processes with picosecond ultrasonic technology. Fig. 2. shows the process flow for RDL formation.

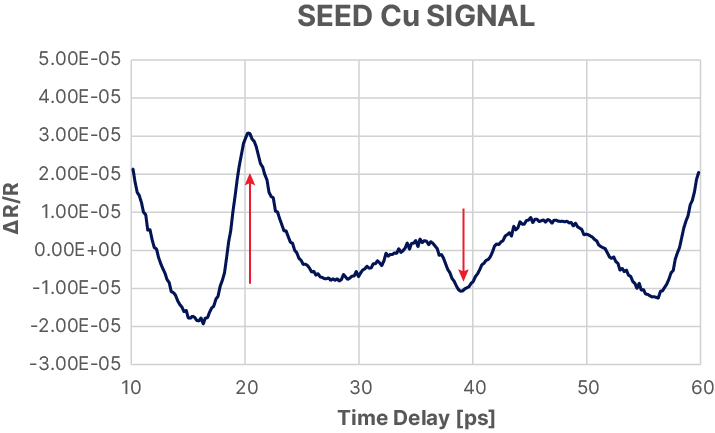

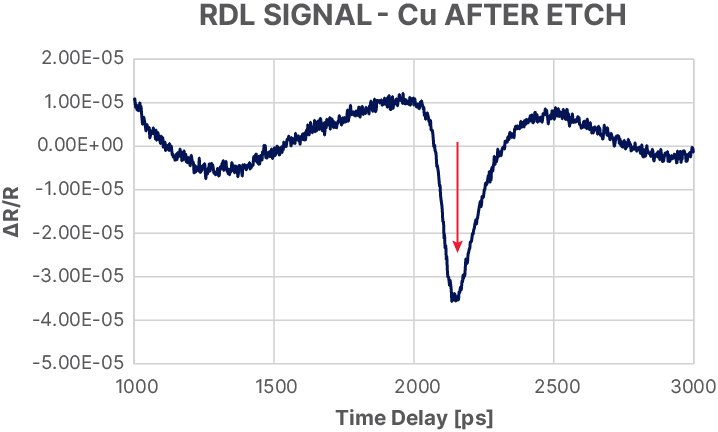

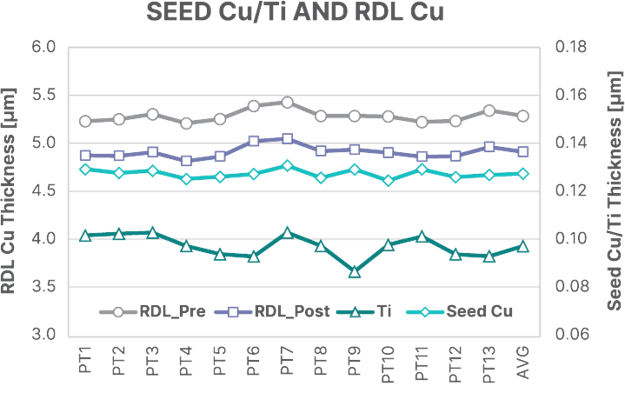

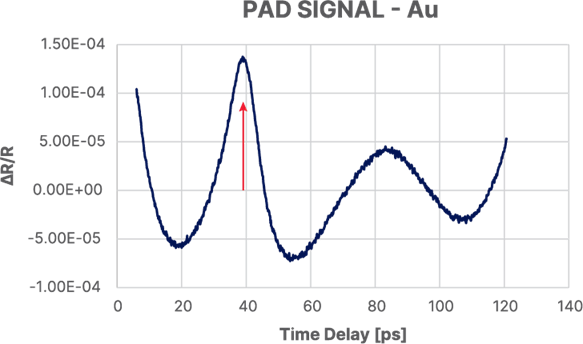

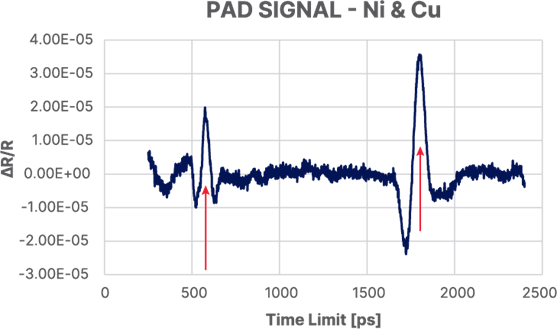

Fig. 3 offers an example of the signal from seed Cu/Ti measured in REF mode and Fig. 4 shows one from RDL in PSD mode. RDL thickness can be measured both in pre- and post-seed Cu removal; 13-point measurement results for seed Cu, Ti and RDL Cu are shown in Figure 5.

The horizontal axis in the signal figures represents the time delay of the probe pulse with respect to the pump, while the vertical axis represents the change of reflectivity (ΔR/R) caused by the travelling acoustic wave. Time zero is the time when the acoustic wave was generated on the wafer surface. The sharp change of reflectivity in the signal, as demonstrated in Fig. 3 and 4, is mostly due to the acoustic wave reflected from the film interface returning to the surface. In addition, the position of the peak and trough is shown with red arrows. These arrows are directly related to the thickness of the films, seed Cu, barrier Ti and EP Cu. From the position of the peak and trough, the thickness of each film can be calculated.

For seed Cu and barrier Ti, the repeatability of each layer is 0.3% or less of the thickness for all measurements. This demonstrates that picosecond ultrasonic technology is able to meet the necessary 10% gage repeatability and reproducibility requirements. For RDL Cu, the sharp change of reflectivity near 2,200ps corresponds to the round-trip time of the acoustic wave within the RDL Cu film; Cu thickness can be calculated from the trough position. The sharpness of the trough, along with thickness, indicates the trough position can be calculated with good repeatability. In fact, the repeatability of RDL Cu measurements for each point is less than 0.1% of Cu thickness, once again exceeding the 10% gage repeatability and reproducibility requirements.

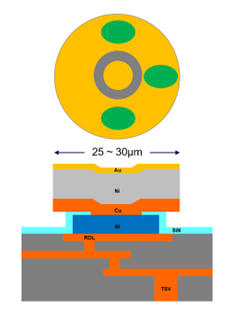

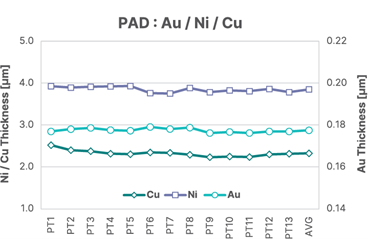

We also used picosecond ultrasonic technology to measure a bond pad whose film stack is Au/Ni/Cu, with Au being the top film. Fig. 6 shows the schematic of a bond pad with a dimple structure, while Fig. 7 shows an example of an REF mode signal from the bond pad with a dimple structure. Note: this pad is used to bond micro-bumps within a die; the typical pad size is 60μm or larger.

Although the height of the center region of the pad is lower than the surrounding region by a few microns, we could successfully measure individual layer thicknesses by measuring a few sites in the outer ring area and selectively choosing ones with good signal-to-noise ratios. This is possible because the focused spot size of the picosecond ultrasonic beam is 8´10µm2, small enough for the direct measurement on the outer ring of the pad.

Measurement on Interposer Pad with Dimple Structure

Fig 7: An example of an REF mode signal from the bond pad with a dimple structure for Au (a), Ni and Cu (b), and a 13-point measurement results for Au, Ni and Cu (c).

In Fig. 7a-b, the red arrows indicate the reflectivity changes caused by the acoustic waves returning from the interface to the surface. With these peak positions, we were able to calculate each layer’s thickness with good accuracy and repeatability. The repeatability of Au, Ni and Cu films for each measurement was less than 0.2%, 0.05% and 0.05%, respectively. As such, all three film measurements outperformed the requirement of 10% gage repeatability and reproducibility.

It should be noted that Au film is much thinner than the other two films. As such, there is a significantly higher repeatability for Au films compared with the other films.

Conclusion

Advanced packaging is a highly complex back-end process that involves a variety of technologies. Interconnection technology is one of the most critical parts of packaging because chips are interconnected through metal lines to receive power, exchange signals and, ultimately, operate. Controlling metal thickness and within wafer uniformity in these processes is critical to meeting the requirements for signal integrity in advanced packaging.

In this article, we have demonstrated that picosecond ultrasonic technology can provide a metrology solution with excellent accuracy and gage capability for the control of interconnect processes in advanced packaging. Based on this information, it becomes increasingly clear that picosecond ultrasonic technology is poised to play an increasingly important role in advanced packaging as back-end processes become more like front-end processes.

Acknowledgments

We would like to thank Sanghyun Bae, Junghwan Kim, and Hwanpil Park of Samsung Electronics Co., Ltd., and Kwansoon Park, G. Andrew Antonelli, Robin Mair, Johnny Dai, Manjusha Mehendale and Priya Mukundhan of Onto Innovation for their contributions to this article.

Cheolkyu Kim, Ph.D., is director of product marketing at Onto Innovation with a focus on application development for picosecond ultrasonic (PULSE™) and inspection technologies. Prior to joining Onto, Kim was a postdoctoral research associate in the Physics Department of Brown University. During his three years at Brown, he spent time researching magnetically levitated superfluid liquid helium.

This article was originally posted in the April/May 2025 issue of Semiconductor Digest.