It is no mystery that the semiconductor industry is always advancing, with specifications becoming increasingly stringent as defects become increasingly more difficult to discover. This is especially true in the case of the most advanced nodes, where ever-smaller flaws and deformities can result in a killer defect.

To solve this More than Moore mystery, you do not need to employ the detective skills of Sherlock Holmes. You need the metaphorical equivalent of the pipe-smoking hero’s magnifying glass to find the particles, scratches, pits and air pockets hiding in the shadows.

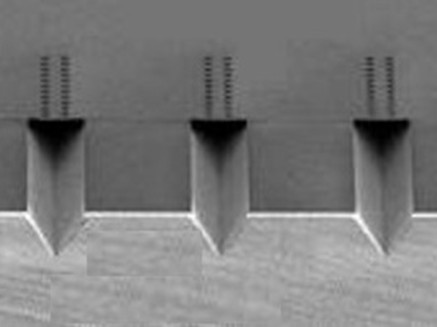

Take the critical dimensions of trenches and vias, for example. As they shrink, the size of a particle or scratch that can potentially result in a killer defect decreases in size as well, making sensitivity an increased priority for bare wafer inspection — on the frontside and backside, at the edge and in the notch.

With an eye on evolving requirements for advanced node bare wafers, manufacturers are seeking inspection solutions with automatic defect classification (ADC) capabilities to perform outgoing quality assurance for wafers, including polished wafers and those with silicon epitaxial layers. Armed with these ADC capabilities, customers can significantly reduce the need for time-consuming and costly manual review.

The frontside, bulk, backside, edge and notch — each of these areas needs to be inspected to ensure the quality of the silicon wafer and the successful fabrication of advanced devices on the wafer. We’ll start with frontside and bulk before moving onto backside, edge and notch inspection, the main focus of this blog.

Wind power. Rail. Solar energy. And, perhaps most significantly, electric and hybrid vehicles. Together, these four forces are among the major demand drivers for power devices.

While silicon (Si) still plays a role in power devices, wide-bandgap compound semiconductors like silicon carbide (SiC) and gallium nitride (GaN) are particularly well-suited for power devices thanks to their higher electron mobility, higher critical electric field and higher thermal conductivity. However, as new structures and larger wafer sizes become the norm for power devices, they bring with them distinct manufacturing challenges.

Today, the industry is transitioning from 150mm to 200mm wafers for SiC- and GaN-based devices and 200mm to 300mm wafers for Si-based devices. The reason: larger wafer sizes may help reduce the cost of fabrication. As the wafer size transition occurs, it is important to have a metrology tool that can measure a larger number of data points across the wafer without impacting the overall fab throughput. A loss of throughput adds to cost-of-ownership and may erase savings earned from transitioning to larger wafers.

Across the semiconductor industry, advanced integrated circuit (IC) substrate (AICS) supplies are low. The causes vary, from a limited number of suppliers who can meet performance requirements, to constrained production capacities, and increased demand resulting from the adoption of high-performance mobile devices, as well as advanced technologies like artificial intelligence (AI) and high-performance computing (HPC). And without question, the ongoing shortage of Ajinomoto buildup film (ABF), a necessary component of many AICS, plays a significant role as well. One area where this shortage of ABF and AICS is having a significant impact is in the manufacturing of flip-chip ball grid array (FC-BGA) packages—the most advanced substrates to meet the electrical and thermal requirements for IC chips with high numbers of I/Os.

To address the substrate shortage, suppliers of FC-BGA substrates are ramping up capacity. However, that acceleration comes with high costs due to the fact that the AICS process is burdened by low yields resulting from the presence of defects that are left undetected by many macro inspection systems. Furthermore, that inability to detect certain defects is potentially magnified as each new layer of ABF on the FC-BGA substrate is built up. In some cases, the number of layers of build-up may reach 20. With each additional layer, the potential for killer defects increases, whether the cause is ABF residue in laser-drilled vias, poor dry-film resist development, or the under and over-etching of Cu seed.

For decades, Moore’s Law has been a way to measure performance gains in the semiconductor industry, but the ability to double the density of transistors on a chip every twoyears is becoming increasingly challenging. With scaling reaching its limit, manufacturers are looking to advanced packaging innovations to extend the performance gains that the industry, and the world at large, have grown to depend on. Cu-to-Cu hybrid bonding is one way the industry is looking to extend ever-increasing I/O density and faster connections, all while using less energy.

Not so long ago, Blu-ray was hailed as a technological advancement in the world of digital video. But in the streaming era, Blu-ray’s luster has faded. However, the technology responsible for the blue laser diode that gave the Blu-ray player its name – gallium nitride (GaN) – is emerging as one of a number of exciting new developments in the semiconductor industry.

Today, GaN is used by the military for radar systems, consumer and automotive electronics as a super-fast power charger and the telecommunications industry in base stations and data servers. GaN offers several advantages over silicon. For starters, GaN offers a significant increase in electron mobility over silicon – 1,000 times more electron mobility, according to various articles – a benefit that leads to other advantages. In addition, GaN is resistant to heat, consumes less energy than other semiconductors, operates at a lower voltage, enables increased miniaturization, offers wider bandwidth and allows for increased electron mobility.

As logic and memory semiconductor devices approach the limits of Moore’s Law, the requirements for accuracy in layer transfer become increasingly stringent. One leading silicon wafer manufacturer estimates that 50% of epitaxial wafer supply for logic will be on nodes equal to or less than 7nm. This is up approximately 30% from earlier in the decade.

To meet the demands of extreme ultraviolet (EUV) lithography, these leading-edge epi-deposited substrates have tighter specifications than previous substrates. Consider 3-5nm logic nodes: the image placement requirement can be as low as 3nm [1].

With the more stringent requirements of EUV lithography in mind, wafer makers are searching for new solutions, such as those addressing the primary reason for inaccuracies in image transfer: macro defects.