Early Zone Correction for Enhanced Overlay Precision in Next-Generation FOPLP Lithography

Abstract

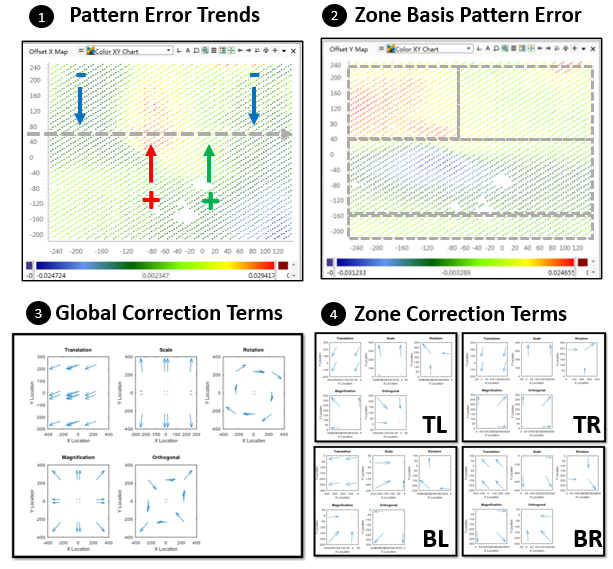

AI chiplet architectures are driving advanced IC substrates (AICS) toward larger panels, finer line/space, and much tighter overlay budgets. This study presents a lithography strategy that combines ultra-large exposure field and fine-resolution imaging with algorithmic early zone correction (EZC) to reduce alignment-solution errors, the largest item in the lithography overlay budget. In this study, we use overlay data from 510 x 515mm panel test vehicles to identify zone-level correctables and apply in-exposure pre-compensation. The approach reduces overlay errors in high-volume manufacturing, improving overlay by 38.2%. The methodology generalizes to ultra-high-density fan-out and 2.5D/3D packaging, providing a practical path to sustain overlay yield for next-generation AICS.

You Have a Challenge? Let’s talk.

We’d love to connect with you.

Looking to learn more about our innovative solutions and capabilities? Our team of experts is ready to assist you. Reach out today and let’s starts a conversation about how we can help you achieve your goals.

Let’s Talk

"*" indicates required fields