Dragonfly® G5 System

The Dragonfly G5 system is engineered for inline process control of leading-edge advanced packaging technologies. As the latest generation pattern inspection system in the Dragonfly series, it delivers unparalleled accuracy in detecting submicron defects and performing high-resolution 3D measurements.

Product Overview

Designed to meet the demands of advanced semiconductor technologies, the Dragonfly G5 system is purpose-built to deliver high-performance, reliable inspection and metrology across complex heterogeneous integration processes. Leveraging next generation high speed line scan 2D imaging and custom-engineered objectives, the system achieves over 3X throughput improvement compared to its predecessor, with submicron sensitivity down to 150nm.

Continuing the legacy of innovation, the Dragonfly G5 system introduces a multi-angle illumination channel that significantly improves signal-to-noise ratio for faint defect detection. Combined with powerful AI-driven algorithms, it enhances both the detectability and classification of critical, yield-impacting defects–empowering fabs to maintain quality and accelerate time-to-yield.

The Dragonfly G5 system expands process control flexibility for wafer-to-wafer and die-to-wafer bonding by integrating high-speed IR imaging to detect sub-surface defects. It incorporates the latest generation of 3Di™ technology, extending bump height metrology capabilities to support next-generation microbumps essential for 3D integration. This enables additional inspection and metrology touchpoints across increasingly complex packaging architectures.

Applications

- Hybrid Bonding

- Redistribution Layers (RDL): after develop, after etch

- BS/FS Pad CMP

- TSV Reveal

- Micro bumps and Cu pillars

Featured News

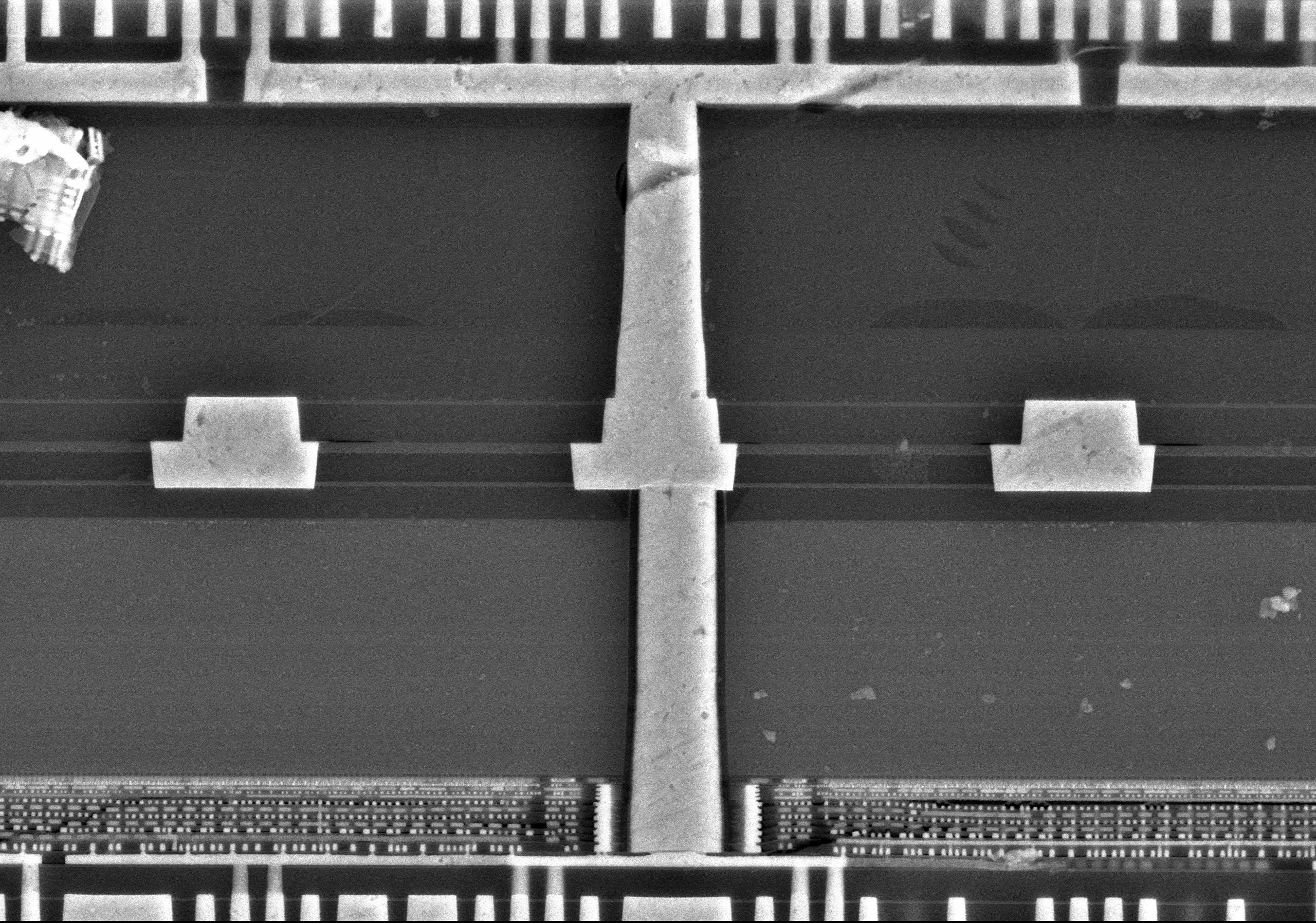

Hybrid Bonding Process Control Solution

Hybrid bonding enables ultra-dense 3D memory interconnects with up to 1,000x more connections than microbumps. Achieving high yield requires stringent process control, including monitoring topography and detecting particles, cracks and voids. Measuring dishing in copper pads provides valuable insight into surface conditions. Together, these process control insights contribute to improved device reliability and performance.

Enabling In-Line Process Control for Hybrid Bonding Applications

As demand grows for high-performance computing (HPC) and AI-driven applications, manufacturers are turning to hybrid bonding to enable the ultra-dense 3D integration required for next-generation chip architectures. This advanced packaging technology presents significant process challenges. Surface preparation must be precisely controlled to eliminate particles, excess recess, and copper pad dishing, all of which can compromise bond quality. During pre-annealing, particle-induced gaps and wide bonding gaps can prevent proper wafer contact. Post-annealing, the formation of dielectric and metal voids introduces further risks to electrical performance and long-term reliability.

Do you have a Dragonfly G5 system question? Let’s talk!

As your partner for innovative solutions, we’re always here for you.

Discover how our cutting-edge semiconductor solutions are engineered to meet your most complex challenges: delivering performance, reliability and innovation where it matters most.

Let’s Talk

"*" indicates required fields

FAaST® CV/IV System

The FAaST system is a versatile, non-contact electrical metrology platform, with an option to combine micro and macro corona-Kelvin technologies together with digital surface photovoltage (SPV). It enables high-resolution dielectric and interface measurements across a wide range of dielectric materials, supporting both R&D and high volume manufacturing.

Product Overview

The primary application of non-contact CV metrology is monitoring dielectric properties during IC manufacturing. Unlike conventional electrical measurements, it requires no sample preparation, eliminating the need for MOS capacitor structures. This reduces metrology cost and enables fast data feedback in both R&D and manufacturing environments.

The corona-Kelvin method uses a corona discharge in air to deposit an electric charge (DQC) on the wafer surface. A vibrating Kelvin-probe then measures the resulting surface voltage (V), enabling determination of the differential capacitance (C= DQC/DV). By monitoring surface voltage in both dark and illuminated conditions, the system separates two key components: dielectric voltage (VD) and semiconductor surface potential (VSB), enabling determination of flat band voltage (VFB).

Analysis of the resulting charge-voltage data yields electrical parameters, including trap density (Dit), flat band voltage (Vfb), dielectric charge (Qtot), dielectric capacitance (CD), Equivalent Oxide Thickness (EOT), leakage current, and tunneling characteristics.

Applications

- Plasma damage monitoring

- Residual charge and non-visual defect inspection

- Diffusion furnace oxide and interface characterization

- High-K and low-K dielectric capacitance

- Mobile ion mapping

- Charge trapping and hysteresis

Featured Markets

Do you have a FAaST CV/IV system question? Let’s talk!

As your partner for innovative solutions, we’re always here for you.

Discover how our cutting-edge semiconductor solutions are engineered to meet your most complex challenges: delivering performance, reliability and innovation where it matters most.

Let’s Talk

"*" indicates required fields

MBIR System

The MBIR system is a revolutionary in-line, non-destructive infrared reflectometry system that enables critical process control of high aspect ratio structures, films and epitaxial structures. It meets the needs of leading-edge customers with its high speed and process coverage.

Product Overview

As more high aspect ratio processes are used in multiple industry segments, there are metrology needs for monitoring of related processes, including dimensions and properties of carbon film hard masks and etched 3D structures.

The MBIR system delivers high-throughput, low COO, non-contact, non-destructive measurements of dimensions and uniformity of layers and etched structures used in integrated circuit manufacturing. The small spot size makes the tool suitable for measurements of scribe line test structures as in-line process control. The unique technology and analysis capability simplifies system calibration requirements and removes the effect of substrate variations for key layer measurements.

While the software contains advanced features for measurement recipe and analysis model creation, it has a user-friendly interface and implementation that allows the fab customers to create and manage the recipe system for MBIR tool fleets.

Thickness map from amorphous carbon film

Applications

- Carbon hardmask used on V-NAND devices and test wafers

- Deep trench etch for CIS and analog device chips

- Doping monitoring of SiGeB and SiP materials

- Film composition characterization

- On-device and blanket wafer materials characterization for EPI process

Featured Markets

Do you have a MBIR system question? Let’s talk!

As your partner for innovative solutions, we’re always here for you.

Discover how our cutting-edge semiconductor solutions are engineered to meet your most complex challenges: delivering performance, reliability and innovation where it matters most.

Let’s Talk

"*" indicates required fields

FAaST® Digital SPV System

The FAaST Digital SPV system provides a fast, non-contact, and preparation-free method for full wafer imaging of contamination in silicon. High resolution maps of diffusion length and iron (Fe) concentration are generated in minutes, setting the industry standard for precision and sensitivity in Fe contamination control, reaching the E7 cm-3 range.

Product Overview

There is no disputing the detrimental effect of metallic contamination on the integrity of the critical gate oxide used in integrated circuits. During high temperature processing, contamination in the silicon wafer often precipitates at the Si/dielectric interface or segregates into the dielectric—both scenarios can cause premature device failure and reduced yield. As device dimensions shrink, the tolerance for contamination decreases, requiring ever-lower background levels of metals like iron (Fe). Over the past 25 years, the IC industry has reduced typical Fe concentrations by more than three orders of magnitude, yet further reduction is essential, especially for applications like CMOS image sensors.

The FAaST Digital SPV system addresses this challenge with industry-leading sensitivity and speed. It provides a fast, non-contact, and preparation-free method for full-wafer imaging of contamination. High-resolution maps of minority carrier diffusion length and Fe concentration are generated in minutes, enabling fabs to detect and control contamination at levels as low as the E7 cm⁻³ range.

Figure 1. Typical background Fe concentration in new IC Fablines (blue) and the state-of-the-art SPV detection limit (red)

Applications

- Ingot qualification

- Outgoing / incoming polished wafers

- Epitaxy

- Cleaning

- Diffusion furnace monitoring

- Rapid thermal anneal

Featured Markets

Do you have a FAaST Digital SPV system question? Let’s talk!

As your partner for innovative solutions, we’re always here for you.

Discover how our cutting-edge semiconductor solutions are engineered to meet your most complex challenges: delivering performance, reliability and innovation where it matters most.

Let’s Talk

"*" indicates required fields

CnCV® System

The CnCV system enables wafer-level characterization of WBG materials without test device fabrication, reducing time and cost. As a mercury-free alternative to MCV, it eliminates contamination concerns. The enhanced Kinetic CV mode with UV-assisted corona charge neutralization achieves high throughput and precision for fast, reliable process control.

Product Overview

The CnCV system utilizes a novel constant surface potential corona charging, which enables the precision required over a large voltage range. The patented technology includes charge- and photo-assisted modes, especially suited for speed and precision on WBG materials and structures, including SiC, Ga2O3, GaN, and AlGaN/GaN HEMT. Additionally, Corona-Kelvin characterization includes electrical properties of dielectrics and interfaces of films on SiC and GaN epi layers. An automated top-side edge contact (TSEC) is also available enabling characterization of WBG on insulating/semi-insulating substrates. Automated bias-temperature stress (BTS) measurements are also available with the CnCV system, providing a fast, noncontact way to quantify the reliability of passivated SiC and GaN.

Beyond typical CV type parameters, the full wafer corona approach allows for QUAD (quality, uniformity, and defect) mapping. The electrical defect imaging, QUAD-EDI, mode is especially designed for SiC. It provides a unique means for quick screening of epi electrical defectivity enabling improvement in device yield prediction.

Figure 1. QUAD-EDI Map on final metallized device wafer after Merged Schottky PiN diode fabrication identifying failed dies.

Applications

- Non-contact epi dopant depth profiling in WBG materials

- AlGaN\GaN HEMT measurements (pinch off voltage & 2DEG sheet charge)

- Dielectric and interface characterization electrical defect imaging in SiC for yield prediction

- Bias-temperature stress (BTS) instability measurements on passivated WBG materials

Featured Markets

Do you have a CnCV system question? Let’s talk!

As your partner for innovative solutions, we’re always here for you.

Discover how our cutting-edge semiconductor solutions are engineered to meet your most complex challenges: delivering performance, reliability and innovation where it matters most.

Let’s Talk

"*" indicates required fields

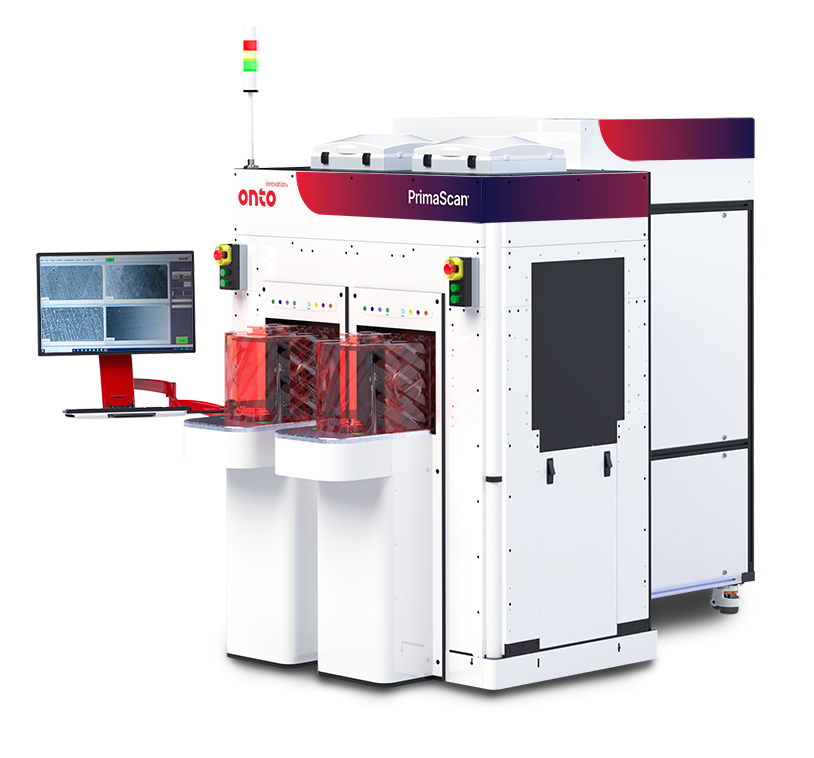

PrimaScan™ System

The PrimaScan wafer defect inspection system delivers a flexible, high sensitivity solution at the lowest cost of ownership per pass.

Product Overview

The PrimaScan system utilizes laser scatterometry and imaging techniques leveraging proprietary optics and sensing technologies for reliable inspection of nanometer sized defects on a variety of opaque and transparent/semi-transparent substrates suitable for either R&D or high-volume manufacturing environments. With multiple detection channels, the system can detect, measure, characterize and image surface particles, scratches, pits, bumps, surface contamination, film or bulk wafer stress, voids/inclusions, including chips and cracks at the wafer edge.

The PrimaScan system addresses challenges in both incoming wafer quality control and in inline process monitoring. Capable of handling multiple substrate materials, it uniquely addresses inline process defect and contamination monitoring in wafer-based production environments.

Designed with versatility in mind the PrimaScan system can handle a variety of wafer sizes and substrate types

Applications

- Opaque or transparent wafer incoming quality (ICQ) inspection

- Process monitor wafer particle and contamination inspection

- Unpatterned blanket photoresist, dielectric or metallic coated wafer defect inspection

- Subsurface defectivity inspection for transparent and semi-transparent films and substrates

- Glass carrier wafer defect and contamination inspection for advanced packaging

- Glass wafer defect and contamination inspection for microfluidics, microlens arrays for AR/VR/MR, flat optics, etc.

Do you have a PrimaScan system question? Let’s talk!

As your partner for innovative solutions, we’re always here for you.

Discover how our cutting-edge semiconductor solutions are engineered to meet your most complex challenges: delivering performance, reliability and innovation where it matters most.

Let’s Talk

"*" indicates required fields