By Cheolkyu Kim, Onto Innovation, and Dae-Seo Park, Samsung Electronics Co., Ltd.

Picosecond ultrasonic technology can provide a metrology solution with excellent accuracy and gage capability for the control of interconnect processes in advanced packaging.

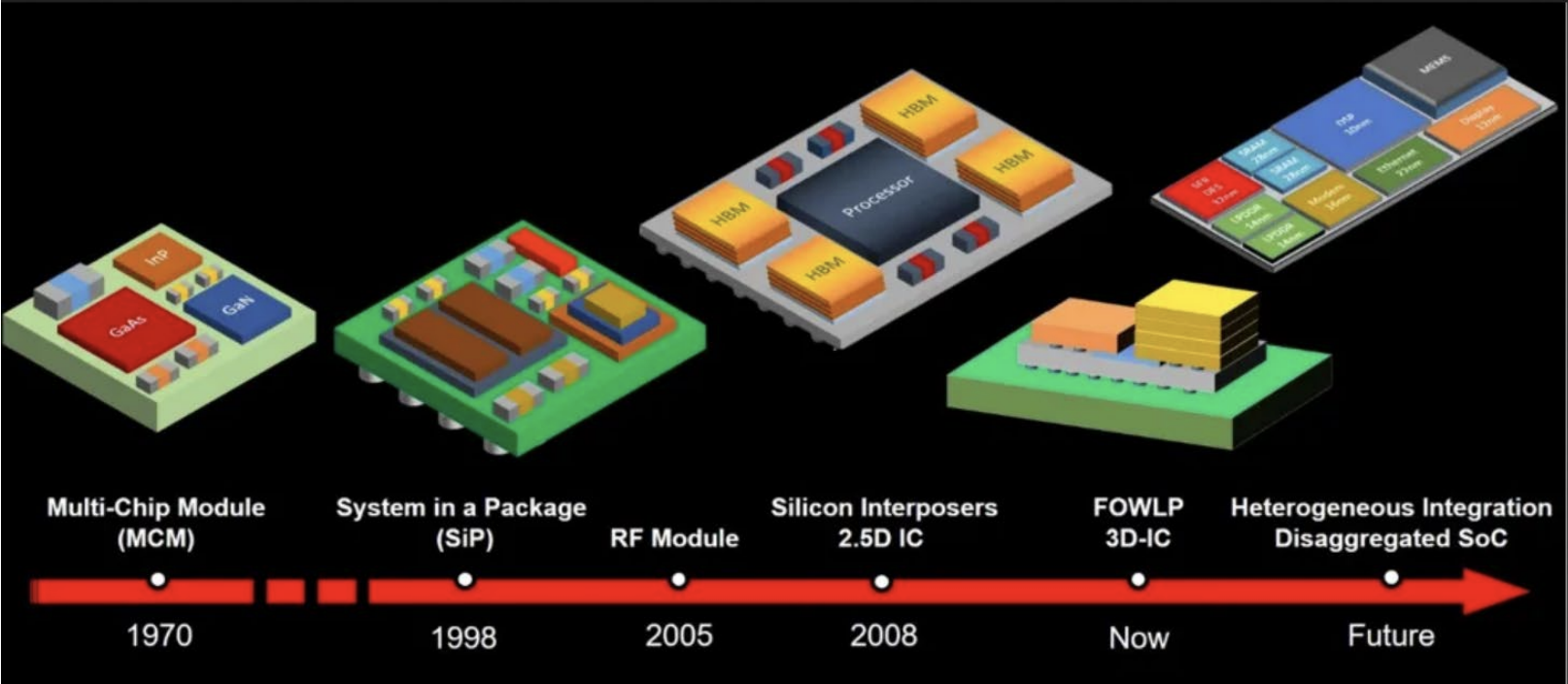

Looking back, 2024 will likely be remembered as a turning point for artificial intelligence (AI). Thanks to the spread of ChatGPT, Microsoft’s Copilot and other large language models, as well as various generative AI tools for video and images, AI has emerged as a tool used by millions of people every day. To create these new high performance AI devices, memory and process chips are packaged together to enable faster communication and lower power consumption. Such devices use advanced packaging technologies like heterogeneously integrated 2.5D and 3D structures.

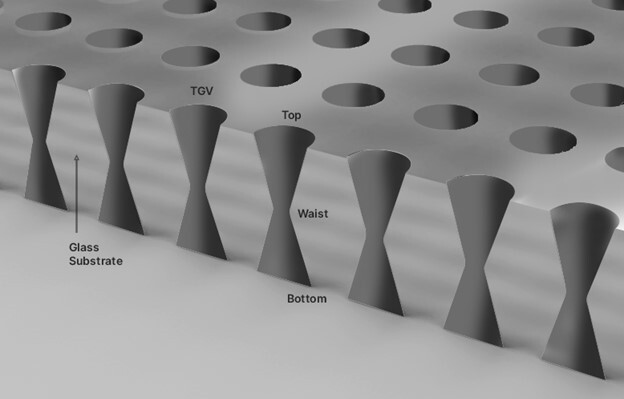

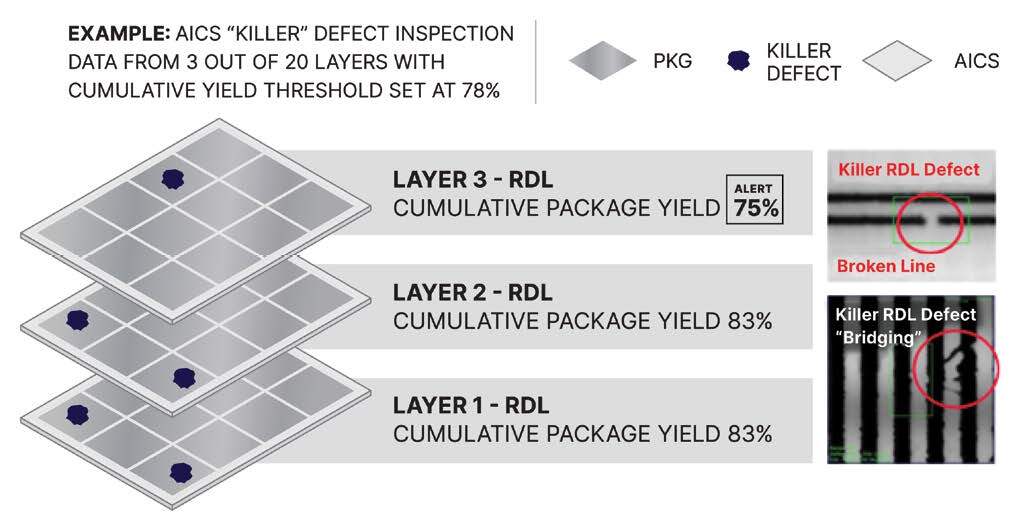

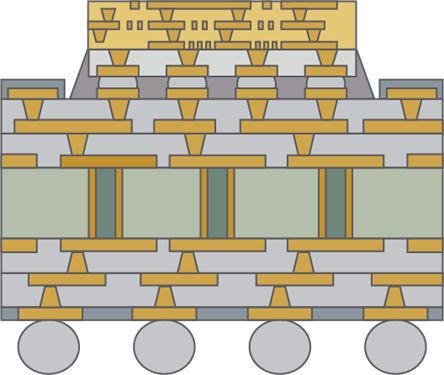

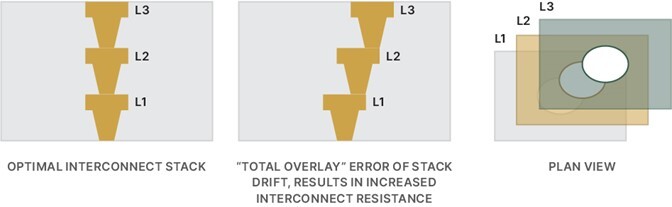

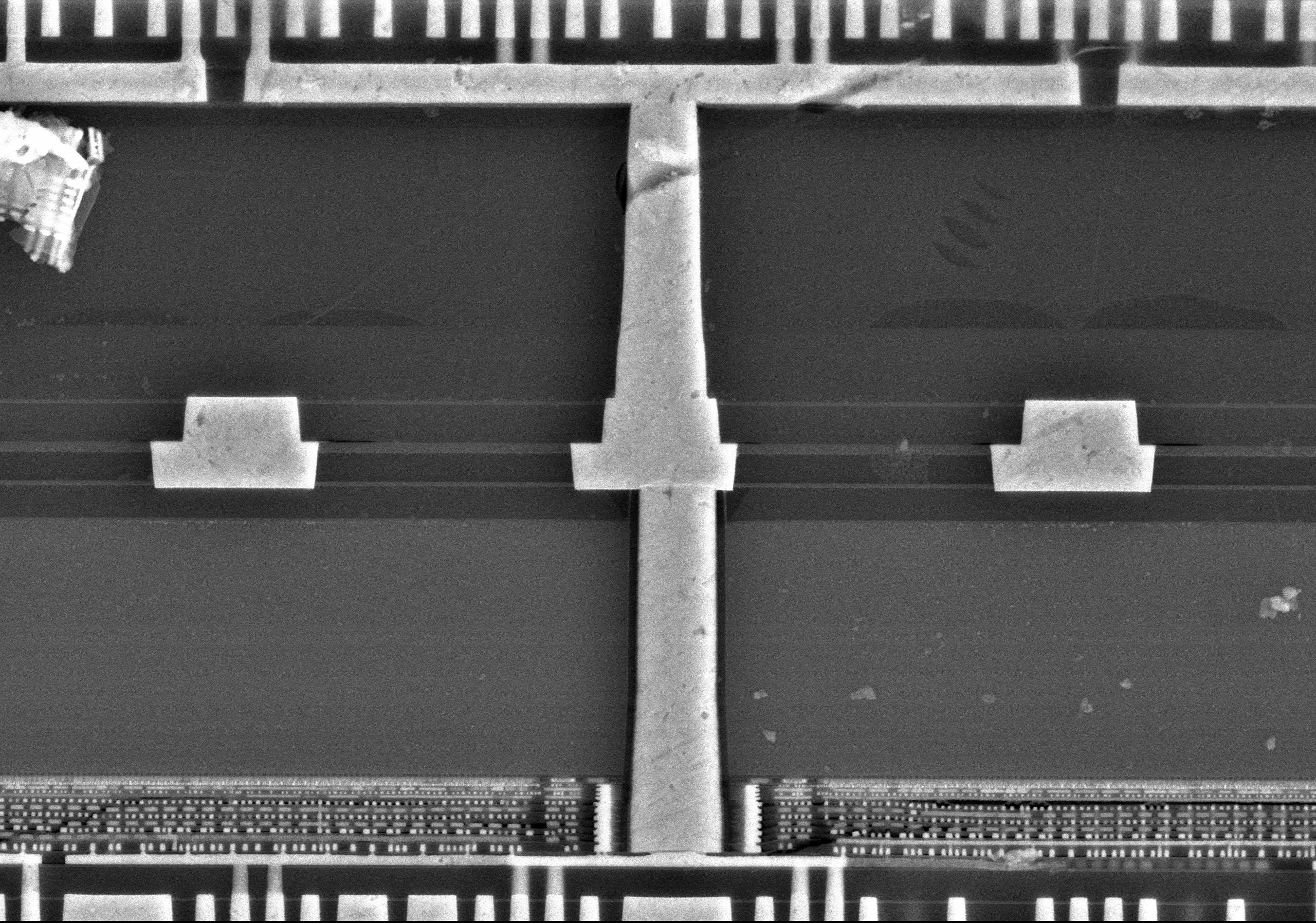

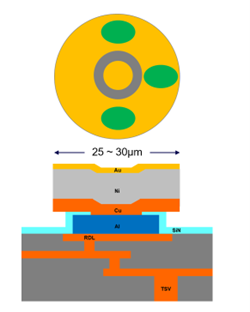

In these 2.5D and 3D structures, conventional memory chips are replaced with high bandwidth memory (HBM) and paired with a graphics processing unit (GPU). The HBM enables the higher data transfer rates needed to handle the significantly increased data processing generated by parallel computation with the GPU. In the latest generation HBM, eight to 12 DRAM chips are connected to each other vertically by through silicon vias (TSV) to form one HBM package. Then four to six HBM packages are connected, horizontally, with the GPU chip by redistribution layers (RDL) on a Si interposer. These new interconnected structures offer significantly improved computing power, latency and higher bandwidth for data transfer and low power consumption as required by AI computing.

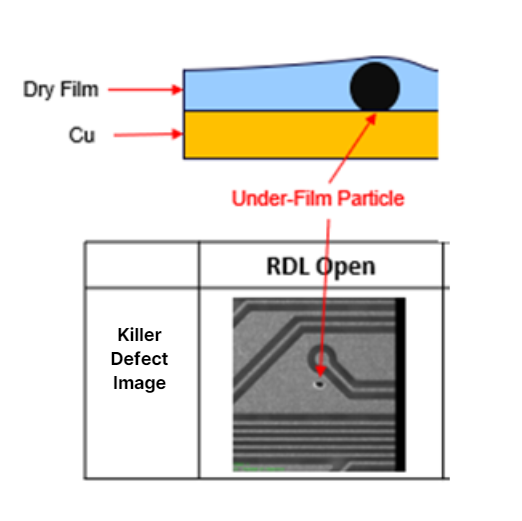

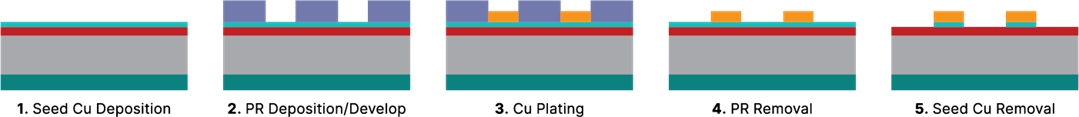

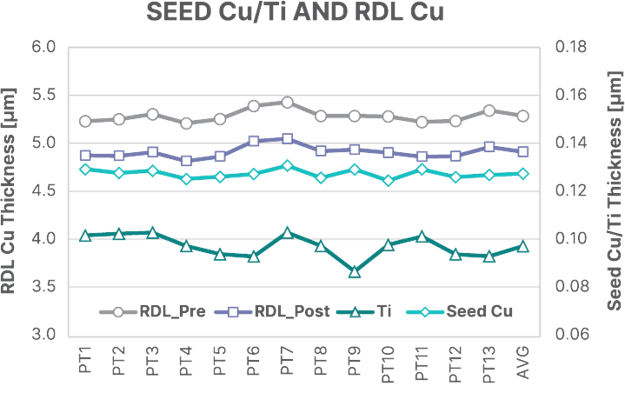

In the case of RDL on a Si interposer, manufacturing multiple layers of RDL is required to handle high data transfer rates. As such, the manufacturing process is much more complex compared to the manufacturing process for more mature packages. Metals, mostly Cu, in RDL are typically deposited using the electroplating (EP) process. The thickness of the metals is affected by the geometric structure underneath, making thickness uniformity control very challenging. To meet the within wafer uniformity requirement for RDL impedance control, measuring and monitoring metal thickness directly on product wafers is crucial. As RDL lines shrink to 2µm or lower – the line/space (L/S) requirements of the most advanced packages – dimensional control is vital to device performance while process control itself becomes even more stringent.

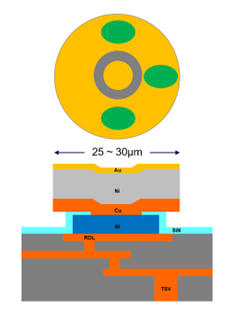

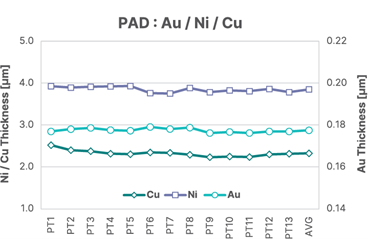

After the final RDL layer on a Si interposer is formed, bonding pads are created. These bonding pads connect with HBM or GPU chips through micro-bumps. Like RDL, bonding pads are also created using the EP process. However, some bonding pads are flat while others possess a dimpled structure. To maintain process control, engineers will still need to measure metal thickness directly on both flat and dimpled structures. In the case of the latter, such measurements are a lot more challenging. To meet these requirements for RDL and bond pad process control, tools enabling in-line metrology on less than 10μm sites are needed. As such, this process requires front-end style process control, with in-line metrology capabilities on a very small site with a very tight process control window.

Picosecond ultrasonic technology has been well adopted in front-end process control, and it can help AP houses better control metal thickness and wafer uniformity to meet device performance expectations. Before we get to that discussion, we will briefly review the traditional packaging process.

Traditional Packaging Process

During the traditional packaging process, metal film measurements are characterized using automated and semi-automated measurement tools such as X-ray fluorescence or sheet resistance measurements. These tools are easy to use and offer low cost of ownership. However, X-ray fluorescence or sheet resistance measurements are not up to the task of measuring multi-layered films or films with varying topographies on product wafers in high volume manufacturing.

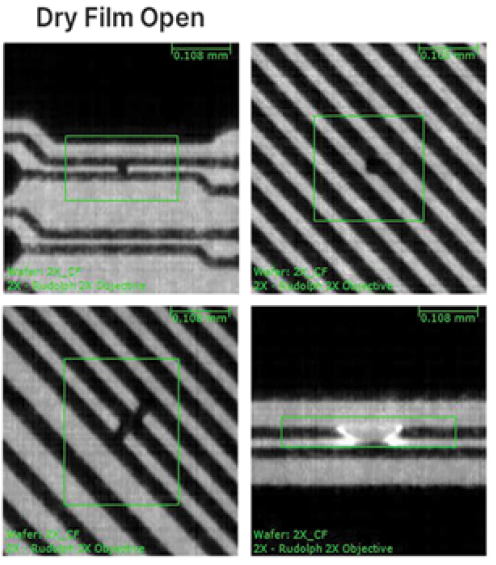

Several commercially available white light scanning interferometer (WLSI) systems are also used in RDL process monitoring. These methods rely on wavelength-dependent interference patterns to provide the step height of metals; this assumes that the step height is the same as metal thickness, which may or may not be true depending on the structure.

As RDL films become thinner, wavelength dependent interference patterns become less sensitive to thickness variation. This affects measurement accuracy. In the case of RDL lines 2µm L/S and lower, the accuracy of thickness measurements becomes even more critical for process monitoring and control. However, WLSI systems have shown limitations in meeting these metrology requirements.

In general, the front-end process must operate inside a window that varies within 10% of the target value. This, in turn, requires a metrology tool with a gage capability (3σ repeatability and reproducibility) of 10% of the variability or 1% of the target value. This metrology tool must be able to measure in-die areas and on test structures smaller than 50µm on real product wafers. Such a tool also needs to be non-contact, non-destructive and fast enough to support high volume production. Picosecond ultrasonic technology enables advanced packaging manufacturers to meet these challenges.

As the AP process becomes more like the front-end process, metrology technology adopted in the front-end will need to be employed. In this article, we will show how picosecond ultrasonic technology can be used to measure metal films during RDL and bond pad processes.

About Picosecond Ultrasonic Technology

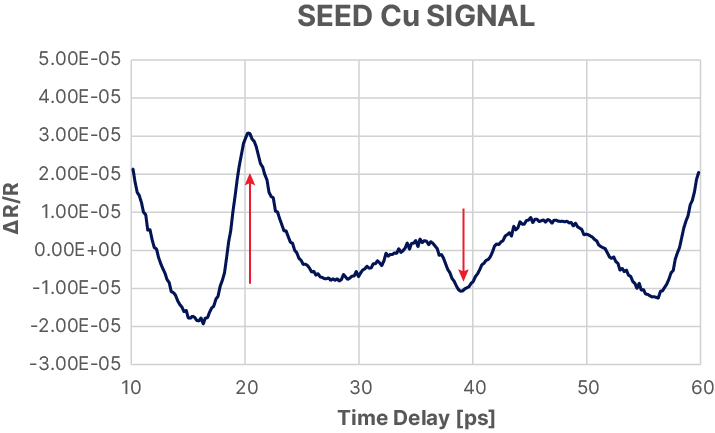

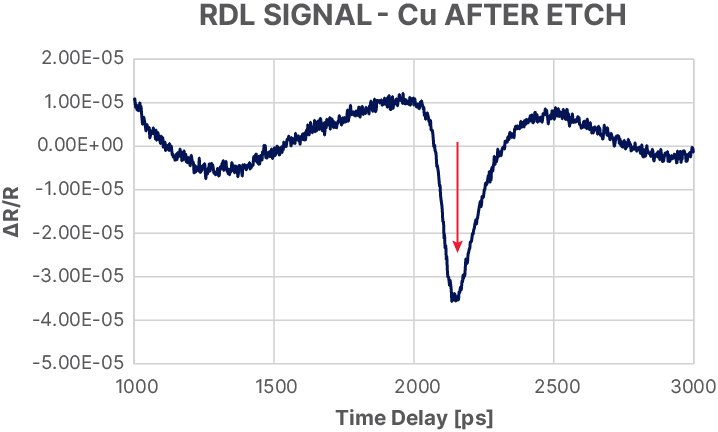

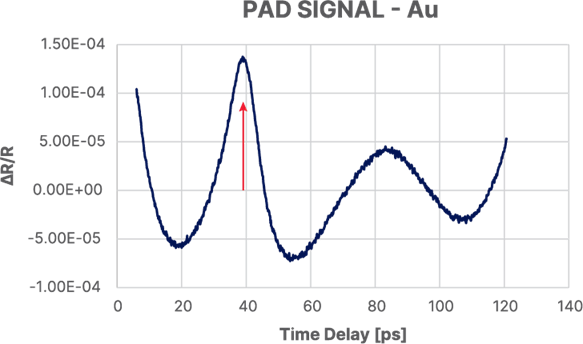

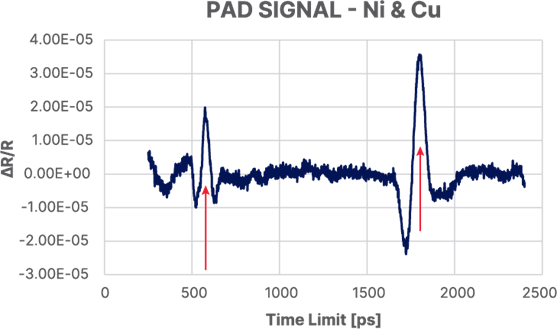

Picosecond ultrasonic technology is a non-contact, non-destructive pump-probe laser acoustic technique used to measure film thickness. This technology measures the round-trip travel time of ultrasonic acoustic waves within film. Using the speed of sound in the material, thickness can be readily extracted using a first-principles technique. Ultrasonic acoustic waves can be generated by a green laser pulse (pump) of 0.2 picoseconds (ps) width that is focused to approximately 8´10µm2. An acoustic wave generated by the pump pulse travels away from the surface through the film at the speed of sound. At the interface with other material, a portion of the acoustic wave is reflected and comes back to the surface while the rest is transmitted. The round-trip time of the acoustic wave can be measured using the time delay between the generation of the acoustic wave and the return of the reflected sound wave after interfacing with other material. The returning wave can be detected using another laser pulse (probe) that splits from the same laser source as the pump. The technique provides accurate measurement of both single-layer and multi-layer metal films.

There are two methods for detecting and measuring the arrival time of the returning sound wave to the surface. One way is to detect small changes in surface reflectivity caused by the density fluctuation of the returning acoustic wave; this is referred to as REF mode. The other way is to detect surface deformation using the returning acoustic wave. Surface deformation can be detected in position sensitive detector (PSD) mode. This consists of two detector cells that are aligned so that the probe beam hits the center of the two detector cells. When the acoustic wave reaches the surface, deformation causes changes in the direction of the reflected probe beam, resulting in a change to the difference between the intensities of the two detectors being measured.

In our study, we used fifth generation picosecond ultrasonic technology to measure the thickness of individual metals on multi-layer structures. This version of the technology features multiple improvements over previous generations. One of the most important improvements for metrology in advanced packaging involves measuring very rough film such as thick RDL.

To measure very rough film, pump beam intensity is modulated at 5 MHz. This modulates the intensity of the acoustic wave it generates. Then the reflected probe beam signal from the detector is demodulated with the same frequency as the pump modulation. This allows for the measurement of extremely weak reflectivity changes caused by the acoustic wave. As the pump beam itself does not convey any information about the travelling acoustic wave but has the same frequency as demodulation, demodulating the signal from the detector may include the signal from the pump. This results in significant noise, especially in the case of very rough films where pump beam scattering is very strong. Fortunately, such noise can be filtered out by further modulating the probe beam at a different frequency, 0.5MHz, and demodulating the signal from the detector with the sum of the two frequencies, 5.5 MHz.

Another significant improvement made to this technology is that the maximum probe beam time delay for the measurement has increased from 5 nanoseconds (ns) to 15ns. This means the maximum thickness that can be measured has increased threefold. For Cu measurement, the maximum thickness that can be measured is now 35μm.

Now that we have discussed picosecond ultrasonic technology, we will turn to our findings.

Measuring Films

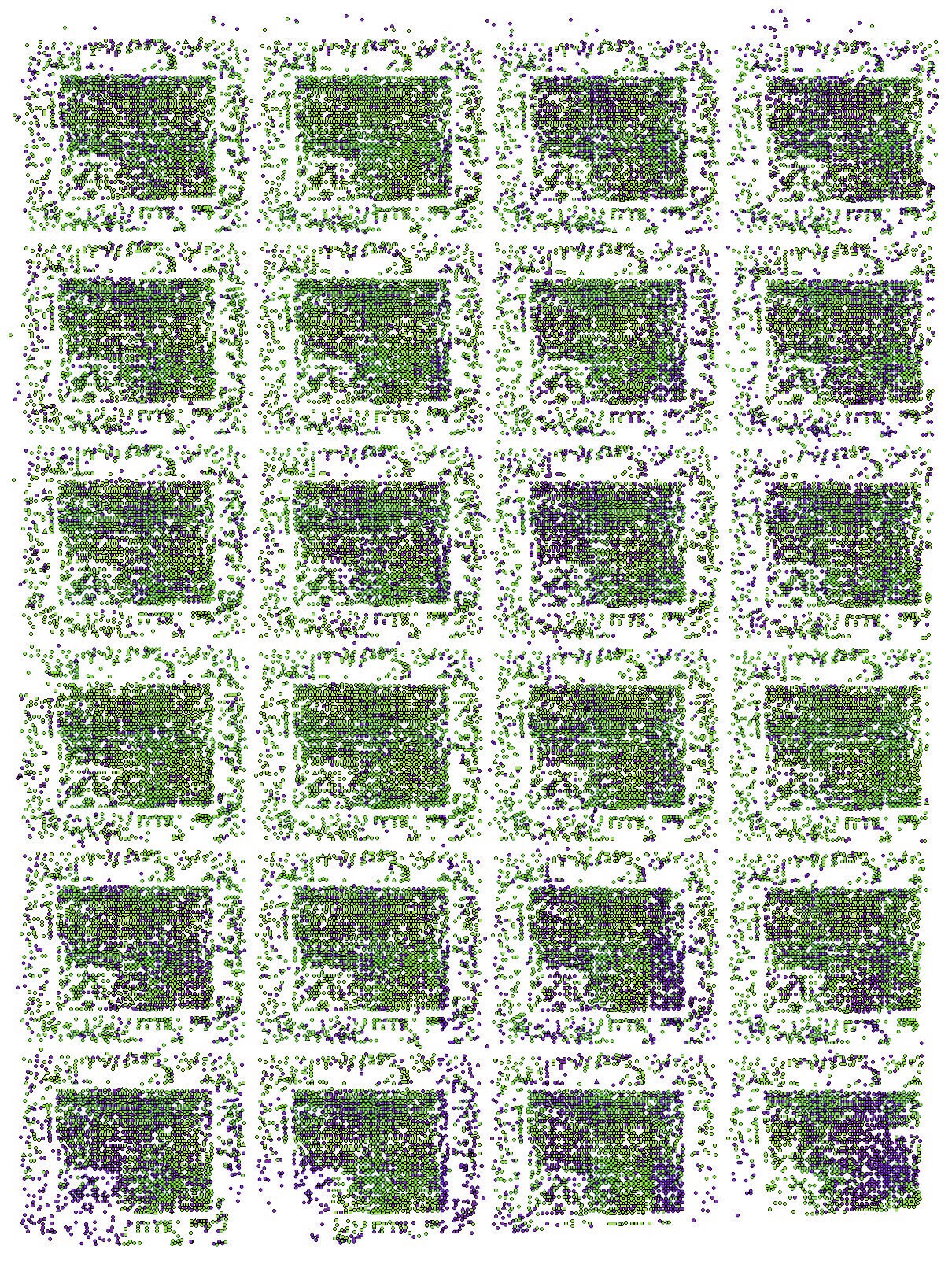

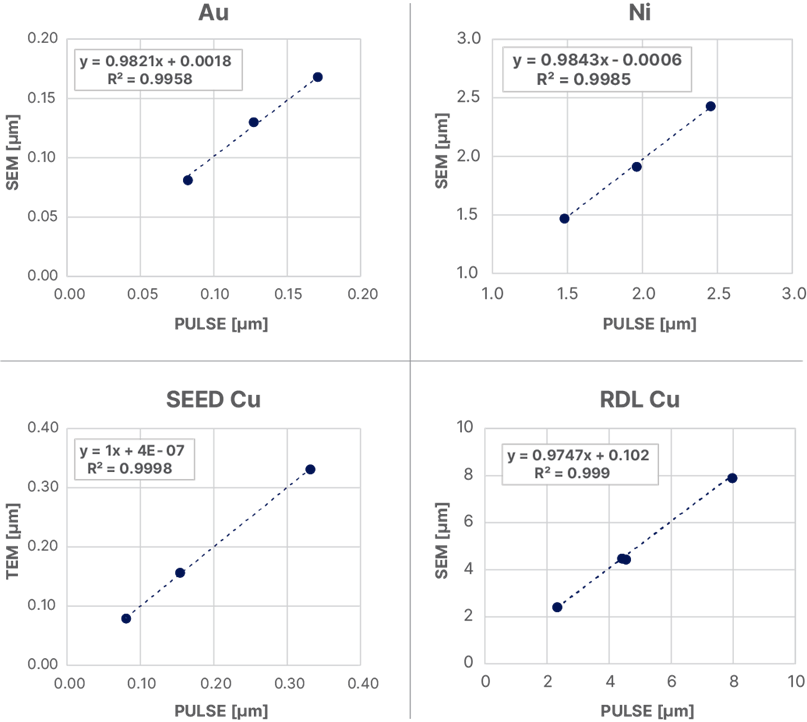

To start with, we conducted a test to confirm the accuracy of picosecond ultrasonic technology when measuring the films typically used in AP: Au, Ni, physical vapor deposition (PVD) seed Cu and RDL Cu (EP). For each film, we used picosecond ultrasonic technology to measure wafers of varying thicknesses. We then cut the wafers for cross-section analysis and estimated the correlation with the picosecond ultrasonic results. Fig. 1. shows the results for the four films. In this scenario, the correlation factor R2 was higher than 0.99 for all four cases, with the slope close to one, clearly demonstrating the accuracy of picosecond ultrasonic measurements.