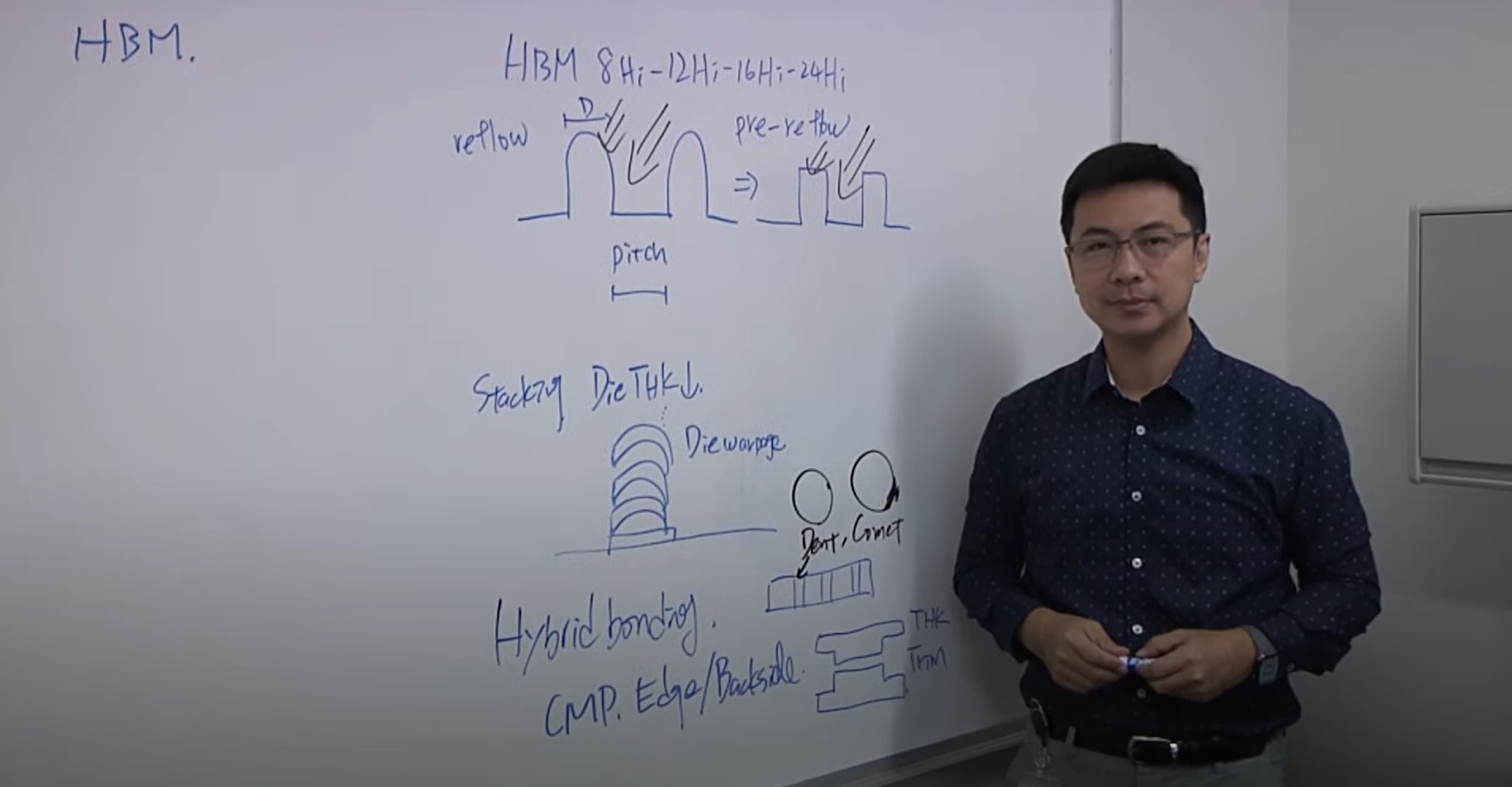

Challenges in Stacking HBM

AI data centers are pushing for higher density in high-bandwidth memory. Today, the maximum number of layers that can be stacked is 8, but that increases to as many as 24 layers by 2030. The big challenge will be in the interconnects, and making sure the microbumps align. At 16 layers, the bump pitch will be less than 10 microns, and the dies will be thinner. Damon Tsai, head of product marketing for inspection products at Onto Innovation, talks with Semiconductor Engineering about how to reduce stress that can cause warpage, how HBM architectures will need to change, and what happens when hybrid bonding and co-packaged optics are added into these devices.

You Have a Challenge? Let’s talk.

We’d love to connect with you.

Looking to learn more about our innovative solutions and capabilities? Our team of experts is ready to assist you. Reach out today and let’s starts a conversation about how we can help you achieve your goals.

Let’s Talk

"*" indicates required fields